Other Parts Discussed in Thread: ADS124S06

Tool/software:

Hello,

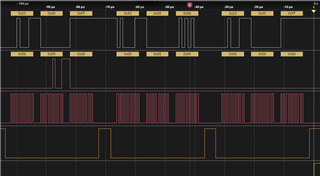

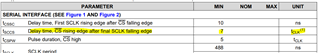

I am seeing random failures on a write to the part in my initialization routines.

All reads always work.

Once initialized - everything works.

However, the write to register Reg3_SYS0 does not always work.

setting = ADS1246_GAIN_32 + ADS1246_SPS_80; // Actually 50 with special clock rate

ADS1246_WriteReg( pCXT, Reg3_SYS0, setting );

result = ADS1246_ReadReg(pCXT, Reg3_SYS0);

if(result != setting)

{

status = false;

}

Any suggestions ?