Other Parts Discussed in Thread: ADS131M08, ADS131M02, ADS131M06, , ADS124S06, ADS131M04, MSP430FG4619

Tool/software:

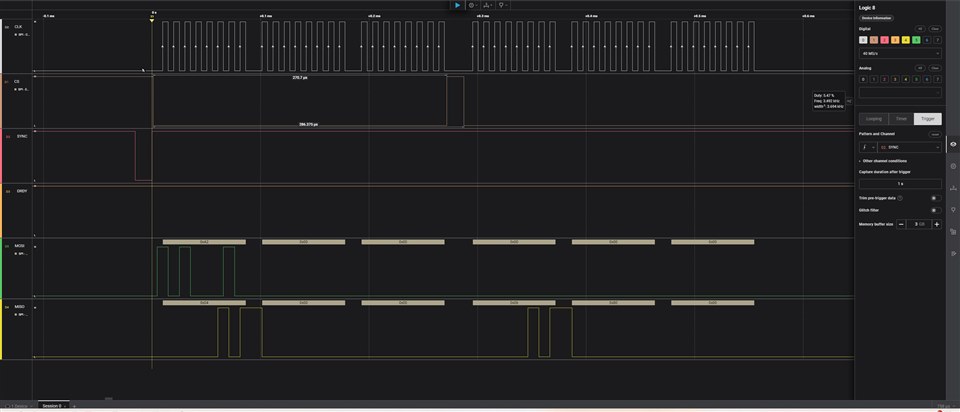

Please see attached scope plots. we can get the ADS131M02 to work but not he ADS131M08.

ADS131M08. DOES NOT WORK

28000 reads analog=0.000 0.000 0.000 0.000 0.000 0.000 volts

first byte returned=28000H=00101000000000000000 is this status register? What is it saying?

ADS131M02 WORKS

first byte=28180 read analog=0.753 0.753 which are correct voltages

first byte returned=28180H= 00101000000110000000 is this status register? What is it saying? Is this reason DRDY stays high?

thanks

Thanks, Peter

Thanks, Peter