Tool/software:

The original thread for this problem was closed as resolved but it is not resolved.

The original problem is that the TI-ADS1261 does not respond in the DOUT line to commands sent to it on the DIN from a Xilinx Zynq 7020 SPI bus. The 1261 is inconsistent in responding to the RESET command which typically fails with silence on DOUT, then after approximately forty attempts the 1261 begins to respond to RESET 0x06, 0xFF with DOUT 0xFF, 0x06. But as soon as the 1261 gets a RREG command using the same bus and same software it stops responding entirely.

Currently I have many of the individual commands working dependably for multiple tests in a row including NOP, RESET, LOCK, UNLOCK.

However, as soon as I attempt to do a RREG command it succeeds for one RREG command then all responses stop from the 1261 including RESET which previously worked. This is true after the RREG no matter how many times I do the RESET. The only way to get the 1261 working again after RREG is a power cycle.

Another thing I’ve noticed that I need to fix somehow is that after power up it takes somewhere between 25 and 100 RESET commands sent to the 1261 before it starts responding. I am not doing anything differently for any command.

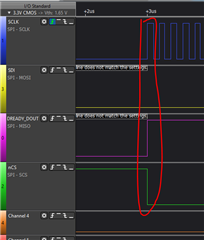

The first diagram below shows a series of spikes which are all good reset commands with responses and which were reported as successful by the software. The second diagram shows a clock level view of the very first reset spike at the clock level. And the third shows a clock level view of the RESET after RREG which is one of hundreds after the 1261 stops responding after the RREG command.

As you can see from the second diagram my clock settings now look pretty good. The bus clock turns on during transmit and receive and afterwords goes low. It is clear in the diagram that the DIN into the 1261 latches on the clock rising edge so it provides a stable read on the falling edge and the 1261 DOUT looks like it is latching on the clock falling edge, as I think you indicated above.

I also include my full software log file this time. There is nothing proprietary in this file. The log file shows approximately 40 reset command fails until it starts working at line 454 followed by eight successful resets. Then I switch to the commands and the first RREG command is successful at line 483. After that the 1261 does not respond to anything. Keep in mind my software is exactly the same for the pass and fail RESET and RREG.

I need help uncovering the reason that the 1261 would delay responding to RESET as well as the reason why it would stop responding after getting the RREG command?