Tool/software:

Hello,

We are using the ADS1298 and are having some issues with implementing leadoff detection.

We set up leadoff detection for DC, using the threshold of 95% and 5%, 12nA, and pullup/down mode.

We are finding that the EEG signal is no longer usable in this configuration, which is doubly unfortunate because the leadoff works great. Is this to be expected? Our input conditioning is just an RC LPF. Is there something else we can try?

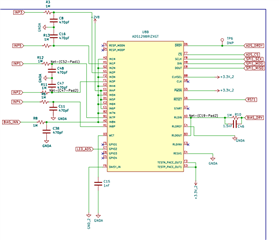

Here is the schematic for the EEG:

Here is the code that sets all the ADS registers: