Tool/software:

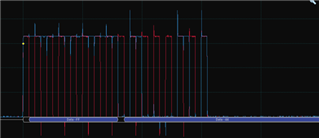

I was having an issue reading the final DOUT bit from ADS1261 to ESP32S3, it was always coming back LOW. Using a picoscope:

We can see that after the final falling edge of SCLK (RED), DOUT (BLUE) goes LOW immediately.

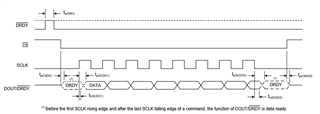

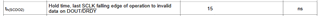

Looking at the datasheet, we can see that the valid time that DOUT is held for after final falling clock edge is th(SCDO2)

th(SCDO2) minimum is 15ns, so we must account for this possibility.

Using Espressif IDF Framework, I cannot determine when precisely data is read in, but I do have it set to SPI Mode 1 as per ADS1261 datasheet.

Now, I found a workaround. By setting my SPI clock frequency to 50MHz, the time from the falling edge of the clock to the next rising edge is 10ns.

This forces the ESP to "read the bits faster". This means that the ESP32S3 is reading within the minimum 15ns time.

However, looking at the datasheet again, the minimum stated SCLK period is 97ns. Using 50MHz, the SCLK period is 20ns.

Despite this, it still works and I haven't seen any broken communication yet. However, I would like to operate within the specified timing requirements.

I would like some clarification that my thoughts are correct. It seems strange that this chip would allow SPI communication down to 1kHz but on the last falling edge would force you to read the bit within 15ns or risk incorrect data.