Other Parts Discussed in Thread: ADS1292R, ADS1298, ADS1293

Tool/software:

Hello TI Team,

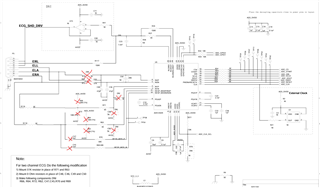

I’m currently evaluating the ADS1291 using the ADS1x9xECG-FE development board, which originally comes with the ADS1292R. For my use case, I’ve replaced the ADS1292R with the ADS1291 and made corresponding hardware modifications to work with channel 1 only. I’ve attached the updated schematic for reference.

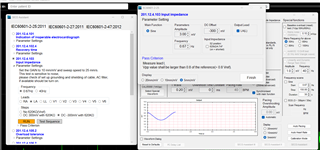

The board is powered with a unipolar 3.0V AVDD, and I’m using the internal reference. The issue arises when I perform the input impedance test using Whaleteq’s SECG simulator, which applies:

-

LA: 1 mV, 1 Hz sine wave superimposed on a -300 mV DC offset

-

RA: 0 mV

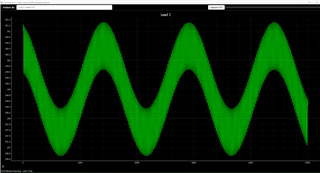

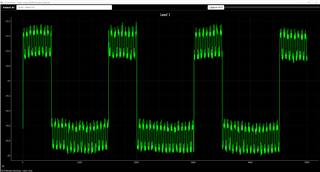

In this configuration, the ADS1291 saturates, and instead of a sine wave, I see a square waveform. Interestingly:

-

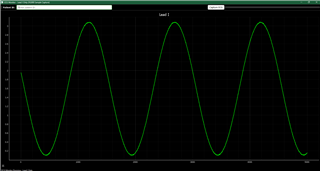

The sine wave is captured correctly if the DC offset is 0 mV or +300 mV.

-

To investigate further, I set the PGA gain to 1 and slowly varied the DC offset.

-

The signal works up to -20 mV DC offset.

-

Beyond -20 mV (even at -24 mV), the output saturates, and I get square pulses.

-

Further observations:

-

If I set PDB_REFBUF = 0 (turning off the internal reference buffer), the saturation issue disappears, but then I observe a constant offset around 2000 mV, likely due to the lack of a stable VREF.

-

Applying ±300 mV DC offset works fine when the reference buffer is disabled.

To isolate the issue, I tested the same SECG setup on:

-

A custom-built board using ADS1298 (also with 3.0V AVDD, internal reference)

-

An ADS1293-based board

Both these setups work perfectly under the same test conditions, with no saturation or clipping.

I’m including the register configuration I’m using for the ADS1291 below for your reference.

Register Configurations:

Could you help me understand why the ADS1291 behaves differently under these conditions compared to ADS1298 and ADS1293, despite the similar setup?

Thanks in advance for your support!

Best regards,

Sajin M.