Other Parts Discussed in Thread: ADC3643

Tool/software:

I'm developing a custom adc3543 board, which is required to have 18bit complex decimation-4 interface at 61.44 Msps.

3 questions I have.

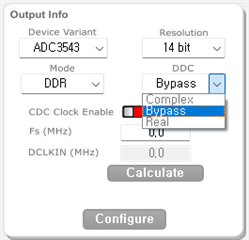

1. In adc35xx EVM GUI, I can't set up ddr mode with complex interface for adc3543.

According to specsheet, It should be possible. Does adc3543 support ddr complex interface?

2. adc3543 specsheet seems to be imcomplete. there's no information about 16bit or 18bit ddr complex mode.

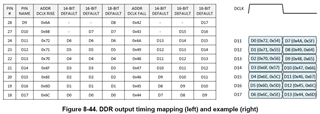

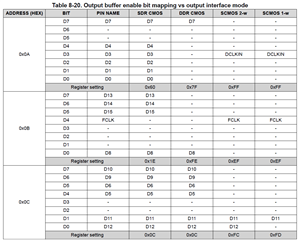

Figure8-44 shows only 14bit ddr real mode. How can I configure output bit mapping for 18bit complex mode?

Additionally, Regarding to Table 8-20, It looks like supporting only 14bit ddr real output.

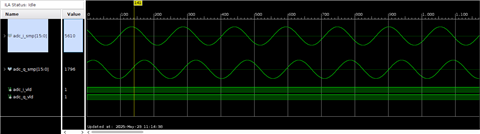

3. provide me with a reference register settings. In EVN GUI, can't get any data. It may be my side problem.

It will be helpful to resolve my issues.

Best Regards

SooHwan Kim