Tool/software:

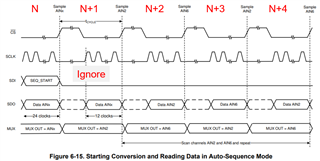

In the SBASA78B – MARCH 2021 – REVISED SEPTEMBER 2024 datasheet/documentation for the AD7067 the section 6.4.4 Auto-Sequence Mode contains diagram "Figure 6-15. Starting Conversion and Reading Data in Auto-Sequence Mode". In that diagram it shows that DAT AINx arrives on SDO in just 12 clocks. Is this a typo? This is a 16-bit ADC and there is no mention of 12 clock size values anywhere else in the document I suspect this is a mistake and that really 24 clocks worth are being received just like in other modes of operation like on-the-fly and manual mode.