Other Parts Discussed in Thread: TSW14J59EVM, , TSW14J57EVM, ADC12QJ1600, DATACONVERTERPRO-SW

Tool/software:

Hello,

we recently aquire two ADC Evaluations boards, ADC12QJ1600EVM and ADC12QJ3200EVM, alongside a data capture board TSW14J59EVM. Using the support system of TI, they recommended the J59EVM as a substitute for the original J57EVM.

We are following the user-guide documentation (slau808 and slau701a) as a first step towards our desired development.

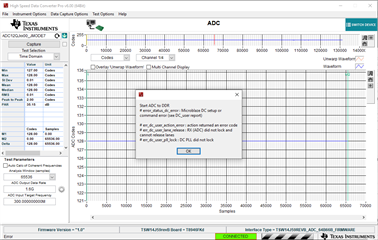

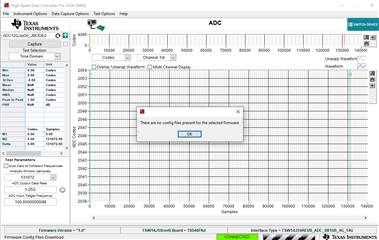

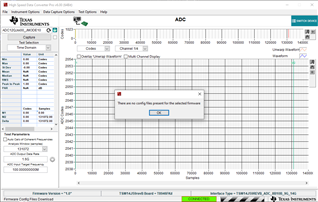

After configuring the ADC Board using the corresponding EVM GUI, and launching the HSDC Pro software, we can load the FPGA firmware but we don't have supported JMODEs (JMODE0) corresponding to the recommended ones in the documentation. Trying to use one of the others available options, after changing the ADC configuration, resulted on the following error message.

The documentation mentions INI files that need to be downloaded and added to the HSDC Pro instal folder, but the files that we could find on the EVM page correspond to the TSW14J57EVM, which uses a different FPGA.

Are those files available anywhere? Does anyone know another workaround?

Thanks in advance,

Fabio Kelm Pereira