Tool/software:

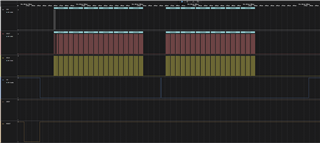

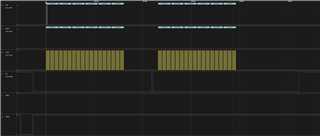

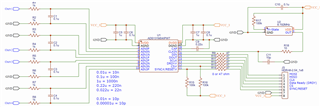

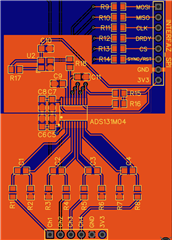

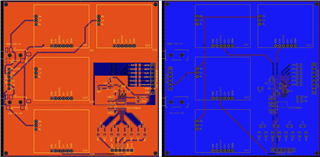

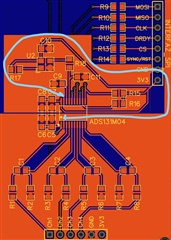

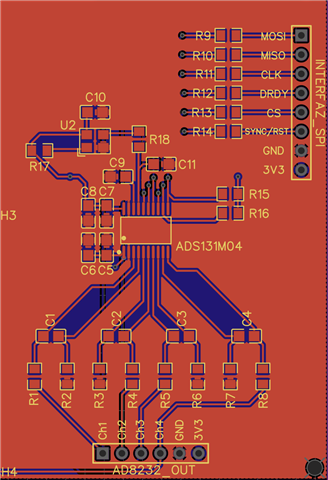

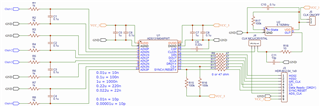

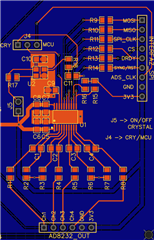

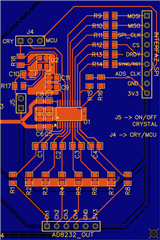

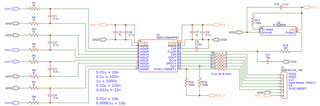

I'm trying to test it with some Arduino code I found on GitHub that supposedly works. So, I'm going to assume the programming isn't the problem. So, I'd like to ask if my design is correct. I built it based on the information in the datasheet and other designs I found online, but I can't get it to work.

Can you tell me if my design is correct?

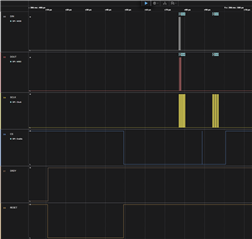

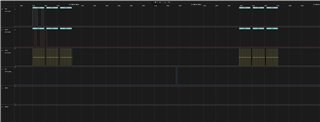

Also, i add a logic test. Here, i was trying to read the ID register (00h), I expected to see the values of bits 15:8, that is, the value (24h), but I get this. Also, I find it very strange that on the MISO line, I see pulses similar to those on the CLK line, but I already checked that they are not connected to each other. In fact, when I send the first bits, the values between the MISO and CLK lines are different. I really don't know why these pulses appear on the MISO line.