Part Number: ADS1292R

Other Parts Discussed in Thread: ADS1292

Tool/software:

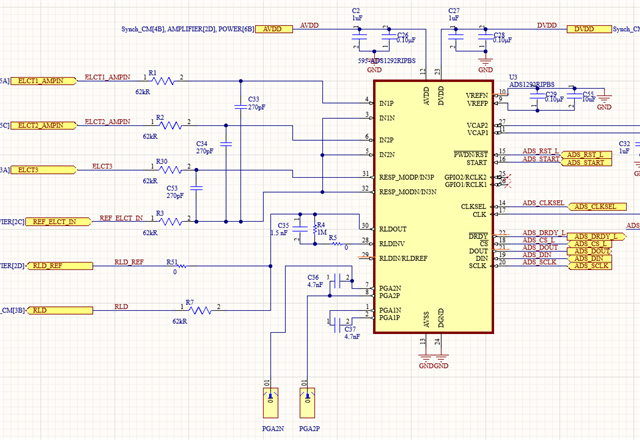

Hello, I am trying to use the ADS1292R to measure EEG signals. Below is the schematic. I am trying to use the RLDOUT using the internal AVDD/2 as the common mode reference for the INP/N input channels. For testing, I am shorting the RLD signal to the REF_ELECT_IN signal to set the common mode for the INP/N signals. Shouldn't this work?

I am finding that the PGA amplifiers appear to get saturated above a common mode voltage of ~0.6V. If I use a common mode voltage lower than 0.6V (by using an external reference for the RLD buffer) it seems to work fine. Is there something wrong with the schematic?

I thought maybe it was because I am tying all of the INN pins together, so I isolated channel 1, but it didn't help.

Some other odd behavior that might be related:

- The reference voltage measured at the VREFP pin is ~ 2.3V instead of 2.42V

- Trying to set the RLDOUT to AVDD/2 results in 3.0V instead of 1.5V

- When trying to read VDD through the MUX in registers 4 and 5 gives ~0V on channel 1 and 2.42V on channel 2.

I would really appreciate help with this.

Thanks

Bob Ozawa