Tool/software:

Hi team,

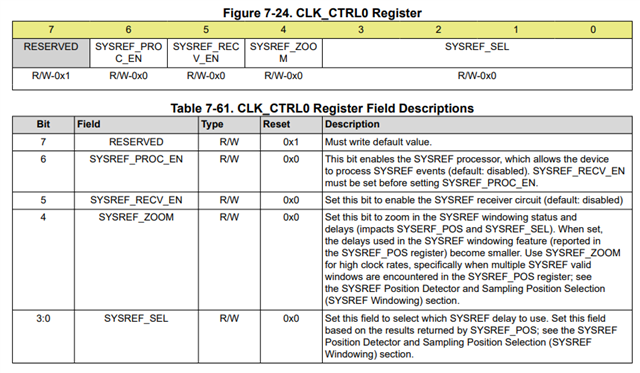

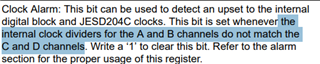

1. According to the description of CLK_ALM, the device monitor whether the internal clock dividers for the A and B channels do not match the C and D channels as below.

But, in case of ADC12SJ1600, the device has only channel A. So can this alarm function work in ADC12SJ1600?

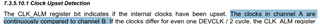

2. According to the description of CLK_ALM, the device monitors internal clock dividers for the A and B channels do not match the C and D channels, while the datasheet mentions " The clocks in channel A are continuously compared to channel B. " according to 7.3.5.10.1 Clock Upset Detection as below. Could you explain this deifference?

3. The datasheet suggests how to enable the CLK_ALM in 7.3.5.10.1 Clock Upset Detection, however, they can't find PD_ACH and PD_BCH as the register bit. Could you tell what PD_ACH and PD_BCH are?

4. Can the function of CLK_ALM detect the unlock of C-PLL?

Regards,

Noriyuki Takahashi