Other Parts Discussed in Thread: ADS1258

Tool/software:

I am reading channels AIN0-15 and all SYSRED channels which comes out to 21 channels in auto-scan mode. from the ADS1258-EP datasheet I calculated my sample rate from the following formula:

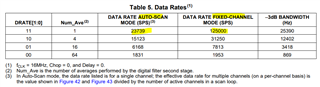

SPS = Fclk / (128 * (4^(11b-DR) + 4.265625 + TD) * 2^CHOP)

Fclk = 14,400,000Hz

DR = 11b (maximal data rate)

TD = 0

CHOP = 0

SPS = 14,400,000/ (128 * (4^0 + 4.265625 + 0) * 2^0) = 21,365

I calculated the conversion latency from the Calculating Conversion Latency and System Cycle Time for Delta-Sigma ADCs document as follows:

Tcl = x / ODR

Where x is the sinc filter order and got:

Tcl = 5 / 21,365 = 234us

Meaning that the latency for converting all channels should be 21 * 234us = 4914us. However, when I benchmark the software it takes only 2546us and all the samples come out correct.

Here is an example in pseudo code for what is being done:

// Benchmark starts here

CS PIN DRIVEN LOW

FOR CHANNEL in CHANNELS

{

PULSE CONVERT

DO {

CHANNEL READ COMMAND

} WHILE NEW BIT != 1

}

CS PIN DRIVEN HIGH

// Benchmark ends here

Is this ADC's conversion latency lower then the formula or am I getting something wrong ?