Tool/software:

Hello,

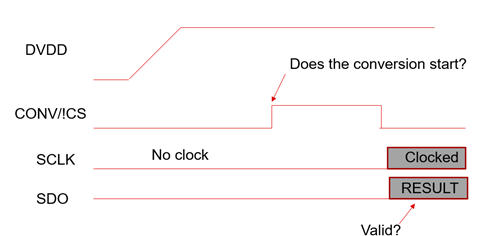

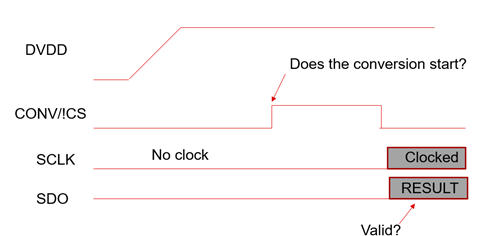

Right after power up, if the default register setting is OK, does just rising edge of CONVST/!CS start the conversion even though no SCLK is received before the rising edge like the below?

Regards,

Oba

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello,

Right after power up, if the default register setting is OK, does just rising edge of CONVST/!CS start the conversion even though no SCLK is received before the rising edge like the below?

Regards,

Oba

Hi Oba,

The rising edge of CONVST opens the sample and hold switch, locking whatever voltage is on the sample/hold cap for the conversion process. The conversion clock is internal - see 7.4.2.3 of the datasheet.

Hello Tom,

So right after powering up, if there is eough CONVST low period for ACQ before the rising edge of CONVST, the conversion should be valid.

No SCLK is needed for it. Correct?

Regards,

Satoshi Obata

You only need SCLK to clock out the conversion results. Assuming the analog input is fully settled and there is adequate acquisition time, the first conversion would be valid.