Tool/software:

In a 15-year-old design, we discovered that the analog buffer for data acquisition was too slow. Now we want to extend the data acquisition time in a simple way.

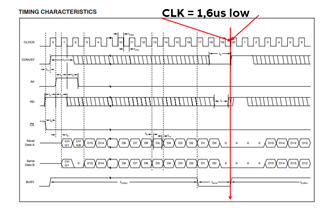

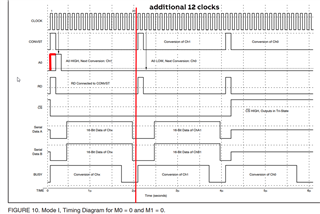

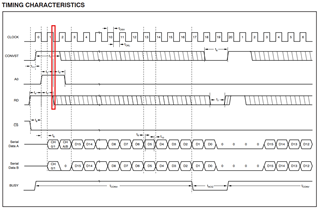

Timing: Clk Periode: 125ns

M0, M1 = low

For data acquisition, we want to increase the time from 400 ns to 2 us.

1) Can we create 16 additional CLKs before the next conversion start?

2) Can we insert a low pause of 2 us at CLK19 and then continue with the conversion start.