Other Parts Discussed in Thread: LMX2594

Tool/software:

Hi,

I am trying to phase synchronize the outputs of two ADC12DJ3200 IC's.

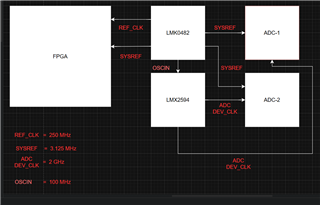

I configured the ADC12DJ3200 to JMODE-6 (8-bit, 4-lanes, dual channel) by setting the following parameters-

Sampling Frequency = 2 GHz

ADC dev_clk = 2 GHz

line rate = 10 Gsps

JESD ref_clk = 250 MHz

SYSREF Frequency = 3.125 MHz

I have set K = 32 and RBD = 28. I am generating the JESD_ref_clk and sysref from LMK0482 and the ADC clocks from LMX2594. The clocks to both the ADCs are fed from LMX2594 and the sysref

to both the ADCs is fed from LMK0482. The clocks are monitored in the scope for different power cycles and observed to be synchronized.

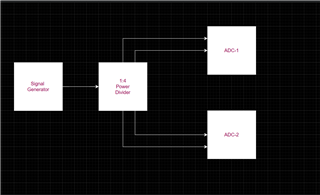

The ADCs are fed with 900 MHz input signal. When the ADC outputs are plotted, it is observed that the channel outputs within the ADC are synchronized and the outputs between the ADCs are not synchronized.

I tried the SYSREF POSITION DETECTION method for synchronization. The sysref position capture values of two ADCs are different and the values of one of the ADCs is varying from run to run.

ADC-1 -----> The sysref position capture values are

0x02C = 1D, 0x02D = 07, 0x02E = 9C

ADC-2 -----> The sysref position capture values are varyng for this ADC.

Most commonly observed values are

0x02C = F1, 0x02D = FE, 0x02E = D9 and

0x02C = F1, 0x02D = FB, 0x02E = FB

It can be observed that the second bit is always zero for the above cases. So, I configured SYSREF_SEL register to 1 (as second bit corresponds to 1 in [7:0]). I plotted the ADC samples again

and observed the same as before. The outputs from ADCs are not phase synchronized though channel outputs within the ADC are synchronized.

I also tried the AUTOMATIC SYSREF CALIBRATION method. I have made the SYSREF_SEL reg to '0', configured the SRC_CFG register and then enabled the SRC_EN. I can observe the SRC_DONE = 1.

But still the outputs from the ADCs are not phase synchronized.

Is there anything to be done so that I can get the phase synchronized outputs from the ADCs?

Kindly request you to resolve this issue.

The ADC configuration register file is attached for reference.

ADDRESS DATA

0x0000 0x30

0x0002 0x00

0x0003 0x03

0x0004 0x20

0x0005 0x00

0x0006 0x05

0x000C 0x51

0x000D 0x04

0x0010 0x00

0x0029 0x11

0x0029 0x11

0x002A 0x00

0x002C 0x00

0x002D 0x00

0x002E 0x00

0x0030 0xA0

0x0031 0x00

0x0032 0xA0

0x0033 0x00

0x0038 0x00

0x003B 0x00

0x0060 0x00

0x0200 0x00

0x0061 0x00

0x0201 0x06

0x0202 0x1F

0x0203 0x01

0x0204 0x02

0x0205 0x00

0x0213 0x07

0x0048 0x0F

0x0206 0x00

0x0207 0x00

0x0208 0x00

0x0209 0x00

0x0062 0x01

0x0061 0x01

0x006A 0x00

0x0200 0x01

0x006C 0x00

0x006C 0x01

0x0297 0x00

0x02C0 0x00

0x02C1 0x1F

0x02C2 0x00

ADDRESS DATA

0x0000 0x30

0x0002 0x00

0x0003 0x03

0x0004 0x20

0x0005 0x00

0x0006 0x05

0x000C 0x51

0x000D 0x04

0x0010 0x00

0x0029 0x00

0x002A 0x00

0x0030 0xA0

0x0031 0x00

0x0032 0xA0

0x0033 0x00

0x0038 0x00

0x003B 0x00

0x0060 0x00

0x0200 0x00

0x0061 0x00

0x0201 0x06

0x0202 0x13

0x0203 0x01

0x0204 0x02

0x0205 0x00

0x0213 0x07

0x0048 0x0F

0x0206 0x00

0x0207 0x00

0x0208 0x00

0x0209 0x00

0x0062 0x01

0x0061 0x01

0x006A 0x00

0x0200 0x01

0x006C 0x00

0x006C 0x01

0x0297 0x00

0x02B0 0x00

0x02B1 0x05

0x02B0 0x01

0x02B2 0x00

0x02B3 0x00

0x02B4 0x00

0x02C0 0x00

0x02C1 0x1F

0x02C2 0x00