Tool/software:

Dear Experts,

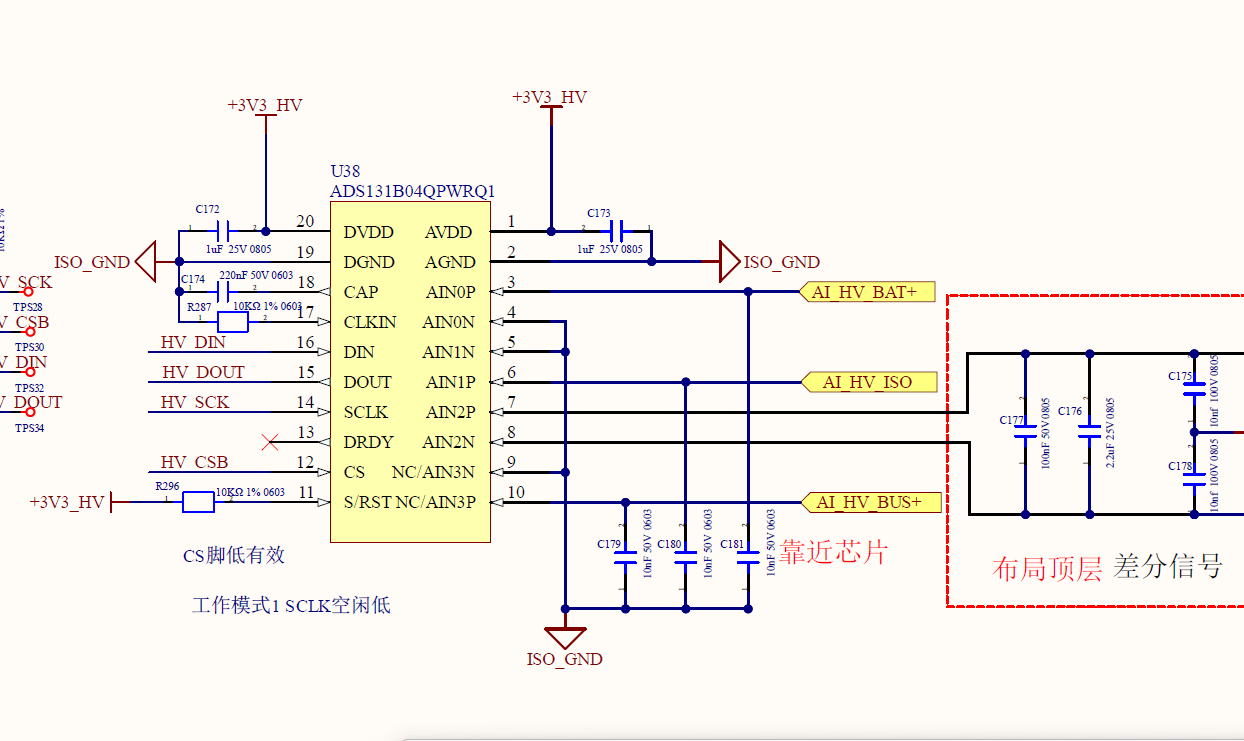

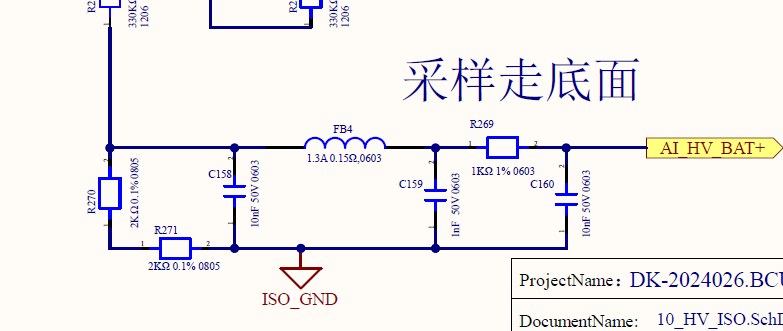

At present, our product is experiencing an abnormal phenomenon during pulse and electrostatic testing. The bus voltage is 200V, and after passing through the peripheral voltage divider circuit, the input ADC AIN0 voltage is 0.1514V.

However, during pulse and electrostatic testing, the input ADC voltage is still stable at 0.1514V. The upper computer displays that the ADC measurement output has changed to 159V. After the circuit is powered off and restarted, the output returns to normal 200V. When tested again, the fault will recur;

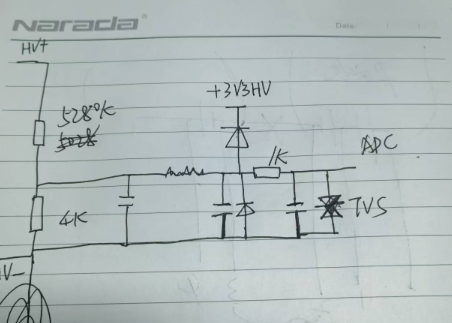

When a fault occurs, we change the bus voltage to 100V, and the output voltage will also change to 79.5V. This phenomenon is very strange, and we would like to ask an expert what the cause of this fault is. Currently, The fault occurred at input port A0, while other ports are normal. It is possible that other ports may also exist, but it has not been discovered yet. The ADC gain is 1, and the circuit peripheral diagram is shown below. Please help analyze it. Thank you very much