Tool/software:

Hi,

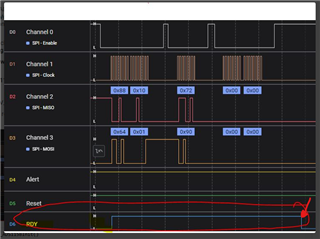

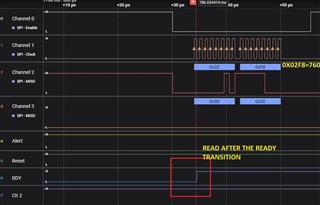

I am unable to read the Data in the ADC channel in the Fixed Channel mode, data is incorrect.

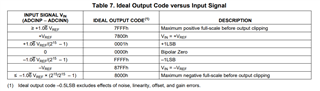

I am applying 0.5V to the Input channel for Channel o, the value is not corresponding to the 0.5V.

Kindly guide me any configuration issue or the Reading method is wrong here.

For the benefit of quick understating and I feel Channel Selection and the specifying the Channel for reading is wrong, but I am not sure, can you put some light on it.

It would be great help, if I find solution here.Thanks in advance.

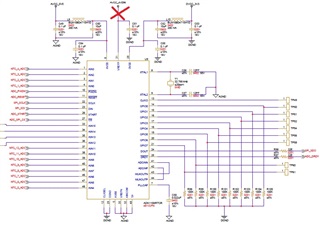

Connection

PWDN & RESET - Pin Pulled Up with 3.3V with 100k

AVDD - +5V

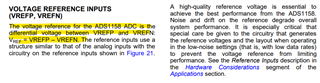

VREFP - Configured for internal Reference in the Software

VREFN - DGND//No need connection if I make internal reference?

AVSS,VREFN,AINCOM - GND

CLKSEL - Not Connected

XTAL1- XTAL2 - 32.768kHz Crystal Connection//Default Connection in the ADS1258EVM Board

DRDY - Controller General Purpose input//Made to monitor the Pin READY up on Data ready

SPI Connection - Standard Connection with the Microcontroller

//Software Configuration

SPI - MODE 0,1Mhz

//Registry Configuration

#define DAQ_DRV_REG_ADDR_CONFIG0 ((uint8_t) 0x00)

#define DAQ_DRV_REG_ADDR_CONFIG1 ((uint8_t) 0x01)

#define DAQ_DRV_REG_ADDR_MUXSCH ((uint8_t) 0x02)

#define DAQ_DRV_REG_ADDR_MUXDIF ((uint8_t) 0x03)

#define DAQ_DRV_REG_ADDR_MUXSG0 ((uint8_t) 0x04)

#define DAQ_DRV_REG_ADDR_MUXSG1 ((uint8_t) 0x05)

#define DAQ_DRV_REG_ADDR_SYSRED ((uint8_t) 0x06)

#define DAQ_DRV_OPCODE_READ_DIRECT ((uint8_t) 0x00)

#define DAQ_DRV_OPCODE_READ_COMMAND ((uint8_t) 0x30) // Includes MUL bit

#define DAQ_DRV_OPCODE_RREG ((uint8_t) 0x40)

#define DAQ_DRV_OPCODE_WREG ((uint8_t) 0x60)

#define DAQ_DRV_OPCODE_PULSE_CONVERT ((uint8_t) 0x80)

#define DAQ_DRV_OPCODE_RESET ((uint8_t) 0xC0)

/* Commands byte masks */

#define DAQ_DRV_OPCODE_C_MASK ((uint8_t) 0xE0)

#define DAQ_DRV_OPCODE_MUL_MASK ((uint8_t) 0x10)

#define DAQ_DRV_OPCODE_A_MASK ((uint8_t) 0x0F)

static void daq_drv_ADS1158Init()

{

// Want to configure the Internal Reference for the Voltage, Single ended ADC, want to read all 16 channels one after the other once ADC read command triggered and Ready pin goes low and High,indicating Ready tor ead the Data

uint8_t l_ucRegDataArray[10];

l_ucRegDataArray[DAQ_DRV_REG_ADDR_CONFIG0] = 0b00100000;//Fixed Channel Mode,Rest all Disabled(SPIRST,

l_ucRegDataArray[DAQ_DRV_REG_ADDR_CONFIG1] = 0;

l_ucRegDataArray[DAQ_DRV_REG_ADDR_MUXSCH] = 0xFF;//Not sure , this should be enabled, no proper description in the datasheet

l_ucRegDataArray[DAQ_DRV_REG_ADDR_MUXDIF] = 0;//Since its not diffrention ADC to be read

l_ucRegDataArray[DAQ_DRV_REG_ADDR_MUXSG0] = 0;//Initially diasbled

l_ucRegDataArray[DAQ_DRV_REG_ADDR_MUXSG1] = 0;//Initially diasbled

l_ucRegDataArray[DAQ_DRV_REG_ADDR_SYSRED] = 0b00100000;//Internal Reference for the ADC is Enabled

// SInce GPIO's are not used Not configured for any pins

daq_drv_WriteMultipleRegisters(0, 7,l_ucRegDataArray);// For to Write Multiple registry

}

static void daq_drv_WriteMultipleRegisters(uint8_t startAddress, uint8_t count, const uint8_t *regData)

{

s_ucDataTx[0] = DAQ_DRV_OPCODE_WREG | DAQ_DRV_OPCODE_MUL_MASK | (startAddress & DAQ_DRV_OPCODE_A_MASK);

memcpy(&s_ucDataTx[1],regData,count);//Copy the dat for Writing Multiple registries

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataRx,(1 + count));//Transmit through SPI

}

static int32_t daq_drv_AdcRead(uint8_t l_ucAdcChId, uint8_t l_ucTimeoutVal)

{

uint8_t l_ucRdyStatus;

unsigned long runningms;

static uint8_t s_ucRegistrySwitched;

//Select Channel

if(l_ucAdcChId < 8)

{

if( s_ucRegistrySwitched )

{

// Clear the DAQ_DRV_REG_ADDR_MUXSG1

s_ucDataTx[0] = DAQ_DRV_OPCODE_WREG | (DAQ_DRV_REG_ADDR_MUXSG1 & DAQ_DRV_OPCODE_A_MASK);

s_ucDataTx[1] = 0;//Clear the Previous Selection of Registry

/* Initiate transfer */

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataRx,2);

s_ucRegistrySwitched = 0;

}

s_ucDataTx[0] = DAQ_DRV_OPCODE_WREG | (DAQ_DRV_REG_ADDR_MUXSG0 & DAQ_DRV_OPCODE_A_MASK);

s_ucDataTx[1] = (1 << l_ucAdcChId);

/* Initiate transfer */

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataRx,2);

}

else

{

if( s_ucRegistrySwitched == 0 )

{

// Clear the DAQ_DRV_REG_ADDR_MUXSG0

s_ucDataTx[0] = DAQ_DRV_OPCODE_WREG | (DAQ_DRV_REG_ADDR_MUXSG0 & DAQ_DRV_OPCODE_A_MASK);

s_ucDataTx[1] = 0;//Clear the Previous Selection of Registry

/* Initiate transfer */

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataRx,2);

s_ucRegistrySwitched = 1;

}

s_ucDataTx[0] = DAQ_DRV_OPCODE_WREG | (DAQ_DRV_REG_ADDR_MUXSG1 & DAQ_DRV_OPCODE_A_MASK);

s_ucDataTx[1] = (1 << (l_ucAdcChId % 8) );

/* Initiate transfer */

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataRx,2);

}

s_ucDataTx[0] = DAQ_DRV_OPCODE_PULSE_CONVERT| DAQ_DRV_OPCODE_MUL_MASK;

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataTx,1);

runningms = xTaskGetTickCount();

l_ucRdyStatus=daq_drv_GPIOGet(s_stGPIOMappings,0);//Check ADC_DRDY_PIN

while( l_ucRdyStatus )

{

l_ucRdyStatus=daq_drv_GPIOGet(s_stGPIOMappings,0);

if( (runningms + l_ucTimeoutVal) < xTaskGetTickCount() )

{

return ADC_ERROR;//Error state

}

}

// Dummy bytes for reading the Data

s_ucDataTx[0] = 0;

s_ucDataTx[1] = 0;

daq_drv_SpiTxRx(DAQ_DRV_SPI_ADS1158_DEVICE_IDX,s_ucDataTx,s_ucDataRx,2);

//printf("\nD:%d",((s_ucSpiDataRx[0] << 8) | s_ucSpiDataRx[1]));

return ((s_ucDataRx[0] << 8) | s_ucDataRx[1]);

}

void main()

{

unsigned char l_ucChannel = 0;

InitDevice();

InitSpi();//SPI - MODE 0,1Mhz

daq_drv_ADS1158Init();

while(1)

{

printf("\n ADC: %d",daq_drv_AdcRead(l_ucChannel, 100));

l_ucChannel ++;

if(l_ucChannel>15)

l_ucChannel = 0;

}

}