Tool/software:

Hi,

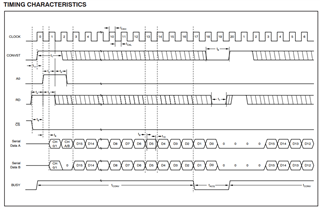

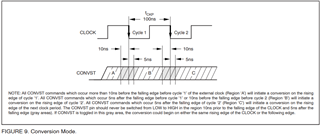

Getting 16 bit data as o/p from ADC instead of 20 bit , given the 20 sclks for reading the values from SPI.

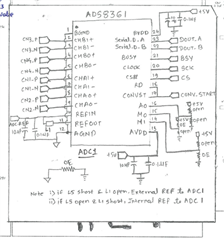

mode pins M0 = 0 , M1 = 1, A0 =0

reference = internal reference 2.5 v

SPI in receive only mode with 10mhz frequency.

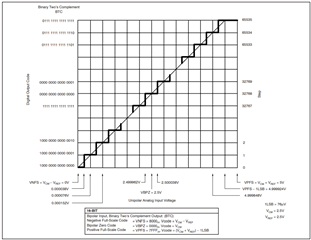

i/p voltage value

1.2744 v 0x8280

1.0021 v 0x65c0

0.5079 v 0x3464