Other Parts Discussed in Thread: ADS7142

Tool/software:

Dear Team TI, I was looking forward to implement ADS7142QDQCRQ1 ADC in my design. I was going through the application note of ADS7142 series ADC and I got few doubts. Can you please clarify the below.

1. In order to calculate Fsamp(max)( which is fs = oscillator frequency/ nclk from data sheet), If tHSO =110ns, then I will end up getting the oscillator frequency of 9.09 MHz. Now if I use High speed oscillator and if nclk is 21 then, fs = 432.9kHZ. Now this violates the maximum sampling speed of the ADC which is 140Ksps. In this case what will be sampling speed fs of the device?

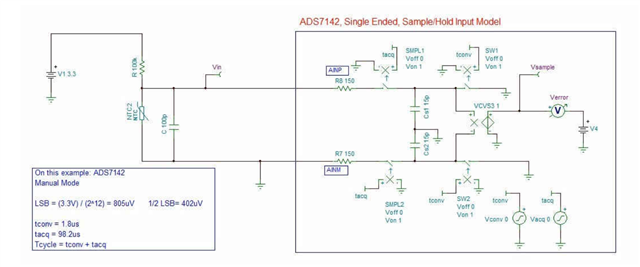

2. Under component selection, point 4 in Application note, I could see that the target sampling frequency is 10KHZ with the max conversion time 1.8 μs. Is this 10kHz the sampling rate which is assumed and to be incorporated in the design.

3. In ordered to get 10kHz as fs, what should I consider oscillator frequency and nclk?

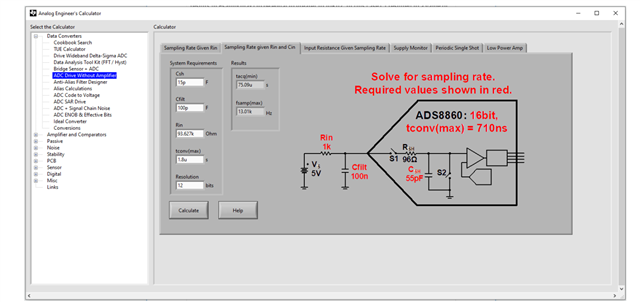

3. In the calculator shown below,

The Rin, Cfilt is not matching with the entered values in the calculator and the values shown in the schematic.

4. Why is Rin not used in the below schematic diagram during simulation? and even though without considered Rin (which was considered for calculating fs based on Cfilt adjustment to get to the nearest value of fs= 10KHz) , C=100pF is considered for the circuit?

Please clarify the above ASAP.

Best Regards,

Srujan L