Tool/software:

Hello!

I am using STM32 device to read data from ADS8665 at 48KHz sample rate for audio application. Unfortunately, STM32 SPI hardware does not provide a functionalty for SPI to get samples at a fixed period. Even though it does, i have to toggle CS pin at 48KHz somehow without CPU intervention. I was using software timer interrupts to generate required CS signal and start a SPI DMA transfer, which involves CPU, leading to inconsistent time period between samples. I solved this recently using 2 different timers.

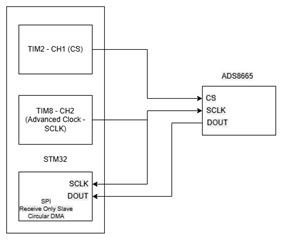

One timer generates CS signal as 48KHz PWM with %20 duty cycle. Other timer works in Trigger mode and when CS timer triggers, this timer generates 16 clock pulses. I used STM32 SPI as slave. Connection is like this:

TIM CLK Signal: Connected to both ADC CLK and STM32 SPI SLAVE CKL

TIM CS Signal: Connected to only ADC CS

ADC SDO: Connected so STM32 SPI SDI

ADC SDI: Low all times

This way, i trick the STM32 as if some master sending data to it, and adc as if master requests data from it. This works but I need an advanced timer of STM32 to provide exactly 16-32 clocks, which can be utilized for more complicated tasks if ADC already handles that itself.

I realized that ADS8665 is capable of providing timer clock from RVS pin, but I have a hard time of this operation of the ADC. If i use it's internal clock, clock output from RVS pin will be very high for my sample rate needs, and this internal clock is not dividable. I wonder if i can provide an external

48KHz continous CS signal with 50% duty cycle

2MHz continuous CLK signal with 50% duty cycle

and ADC outputs samples from SDO, also providing 32 bit clock signal from RVS, so that I can still use STM32 SPI in circular DMA mode by connecting RVS to STM SPI CLK and ADC SDO to STM SDI?

If not possible, is there any way to get ADC samples without CPU intervention?

Thanks in advance!