Tool/software:

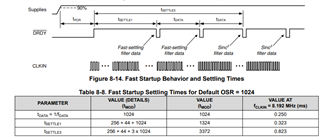

The device is configured to continuous conversion mode for default 4kS/s. I have a DAC output with some lower latency op-amp circuit which is feed to a channel of the ADC (ads131m08). I use a cross-correlation and the latency seems to be the sample period. Ie, about 250µs for the 4kS/s rate. I guess the SINC filters uses multiple readings (OSR) during this period to complete a conversion which is then sent of SPI. I am not concerned about start up conditions, but the 'latency' as per the current conversion (with significant history) against what would be read from a AIN pins. I understand the reading are filtered (so an equivalent filter on the pins).

The DAC and two ADC channels are connected to analog control system. The DAC/ADC1 is the input and ADC2 is a feed back channel on the control output. I wish to observe the delay of the control system (and tracking). I read the Conversion latency in delta-sigma converters appnote (and have other ADCs where explicit conversion diagrams are given). I did not find this for the ADS131M08, but I may have missed it in the data sheet? According to the app note, conversion time and cycle latency might be keywords. The ADS131 seems to only have details on startup and global chop modes (as far as I could see).

Thanks for any help,

Bill Pringlemeir.