Other Parts Discussed in Thread: DAC8760

Tool/software:

Dera support

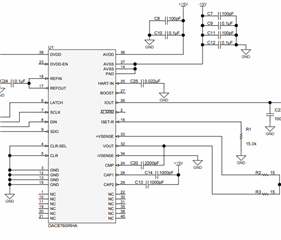

We are designing a circuit for the DAC8750. We have a question regarding unused pins. If we are not using the functions of the ISET-R pin, HART-IN pin, and CAP1 & CAP pin, is it okay to leave them unconnected?

Also, if we are using the internal RSET, is it okay to leave the Control Register DB13 (REXT) setting at its default?

Thank you

Best regards

YUSUKE