Tool/software:

Hi all,

This is my first post in this forum.

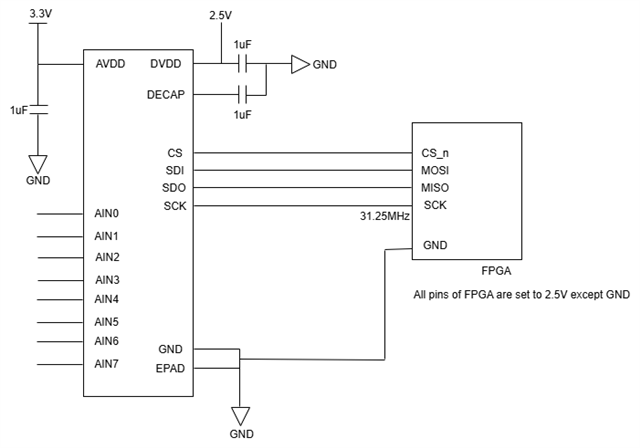

Attached is my circuit schematic. The SPI clock (SCLK) runs at 31.25 MHz, derived from a 125 MHz source clock. I am debugging the design with Signal Tap Logic Analyzer, sampling at 125 MHz to capture the received data; the screenshots are included.

Test sequence

-

Enable on-the-fly mode by sending the 32-bit command

0x08_10_02_00from the FPGA to the ADC. -

Read channel 2 by sending the frame

{2'b10, chan, 7'b0}.

Regardless of the number of attempts, the ADC always returns 0xFFF. I’m trying to determine whether the device is faulty or whether I have missed something in the configuration.

As a cross-check, I connected the same ADC to an ESP32 and tried to read register 0 (SYSTEM_STATUS). It returns 0x00 instead of the expected 0x80 / 0x81.

Could you suggest a systematic way to confirm whether the TLA2518 is working correctly? My ESP32 test code is attached for reference.

Thank you for your help.