Tool/software:

Dear TI Support Team,

I am currently working with the DAC39RF12EVM.

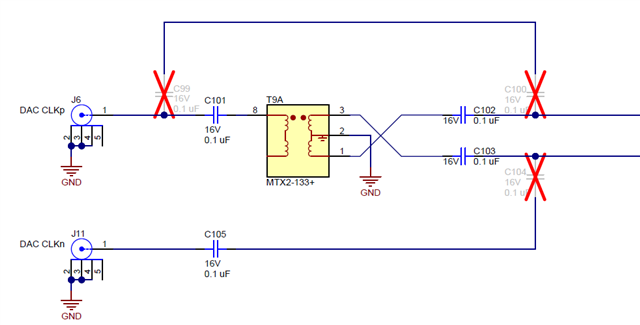

In the default configuration of the kit, the sampling clock is provided as a single-ended signal to the DAC_CLKp port.

I would like to configure the sampling clock input in a differential manner by using both the DAC_CLKp and DAC_CLKn ports.

However, I could not find detailed instructions or guidance for this configuration in the User Guide or Datasheet.

Could you please clarify whether differential clock input is a supported or recommended configuration?

Based on the schematic, it appears that differential clock input might be possible by removing capacitors C101, C102, and C103,

and re-populating capacitors at positions C99, C100, and C104.

Could you please confirm whether this is an appropriate and valid approach for enabling differential clock input to the DAC?

If not, I would appreciate your guidance on the correct procedure.

Thank you for your support.