Tool/software:

Hi team,

Can you use this ADS8686S as an example to teach me how to calculate the total time required for a data to enter the ADC and come out?

And I also have some questions as below:

1. If we want to use two ADS8686S to achieve 16-channel measurement, can we use the same convert?

2. If we share a convst signal, how is the delay of each channel of the second chip calculated, and what are the data at each time?

3. Is there a FIFO inside the ADC? Is the data read from the previous convst? Will it be washed out by the new data? How long does it take for the SPI to fetch the data at the latest after the convst signal ends?

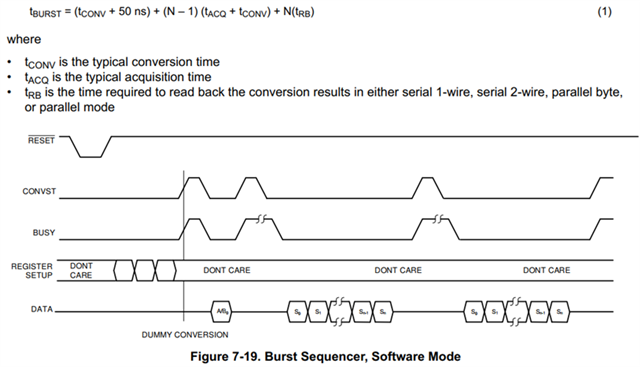

4. In Burst Sequencer, Software Mode, what is the specific calculation of tBURST? According to the formula in the manual: are tACQ and tRB repeated? What is 50ns?

Thanks

Lillian