Other Parts Discussed in Thread: ADC12QJ1600

Tool/software:

(L) Hi,

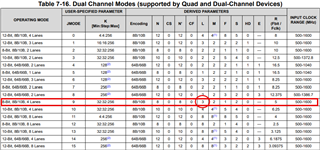

I would like to configure the dual core ADC12DJ1600 in JMODE9, but only use the first core.

How should the FPGA IP be configured to support this? Especially with the lanes (L) parameter?

In a related thread I managed to get a quad device ADC12QJ1600 running with only the first core enabled in the FPGA IP by changing the lanes (L) parameter from 8 to 2.

From the datasheet for a dual device, lanes (L) parameter is specified as 3. Why is that? I would have expected it to be 4??

How should it be changed to cope with first core only running?