Tool/software:

Hello,

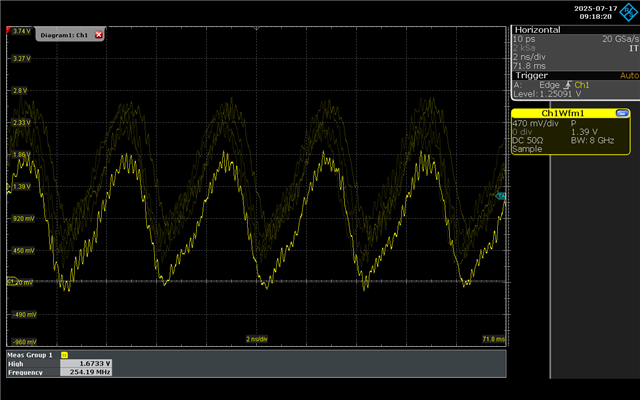

I am expecting the DCLKI output to always have a 50% duty cycle with a frequency of Fs/4 in 1:2 DMUX mode. Can you confirm DCLKI will always have a 50% duty cycle please?

I have a VHDL process that is sensitive to DCLKI and as a test, the process generates a further clock as follows:

p_combine_adc_samples_rising : process(i_DCLKI, reset_n)

variable yy : std_logic := '0';

begin

if rising_edge(i_DCLKI) and reset_n = '1' then

yy := not yy;

gpio(4) <= not yy;

......

Thank you