Tool/software:

Hi team,

I have several technical questions regarding the operation of DAC3171. Could you please kindly answer them?

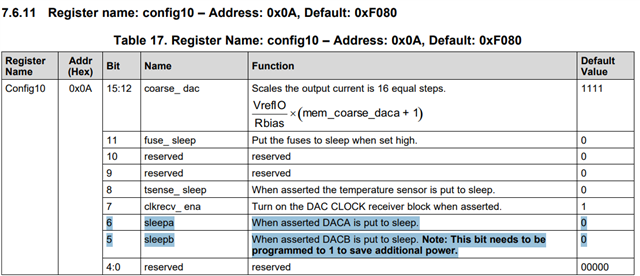

1. How do users configure the power down mode?

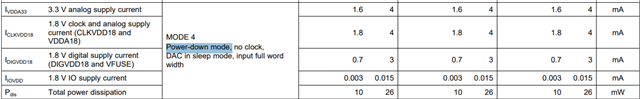

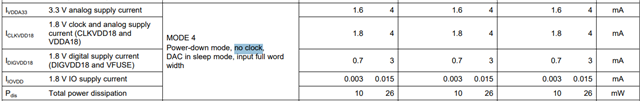

2. No clock means users stop inputting the signals to DAC core Clock(DACCLKP/ DACCLKN)?

3. Are there any configurations which is lower power consumption listed in page 14 of the datasheet(MODE 1, MODE 2, MODE 3, MODE4)?

Best regards,

Shunsuke Yamamoto