Tool/software:

Hi,

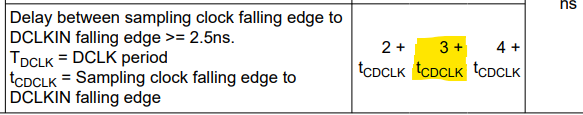

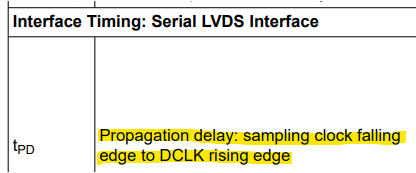

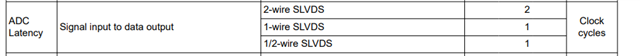

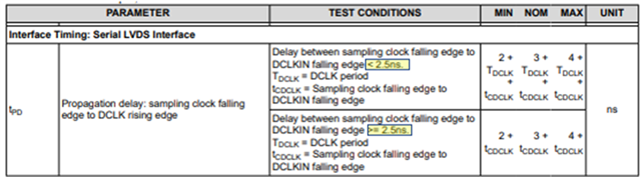

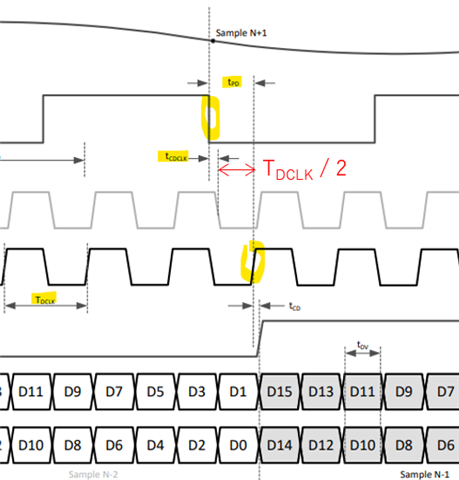

The datasheet of ADC3562 shows the formula to calculate tPD as shown in below.

I think the formula should be

tPD = 3 + tCDCLK + TDCLK/2 (tCDCLK >= 2.5ns)

tPD = 3 + TDCLK + tCDCLK + TDCLK/2 (tCDCLK < 2.5ns)

TDCLK / 2 should be added here.

Is my understanding correct?

PLS refer the following timing chart to understand it.

If my understanding correct, could you revise the datasheet to correct the formulas?

Best Regards, Taki