I'm having trouble getting my ADC to respond with an output. My code pertaining to the ADC is as follows:

P3SEL = 0x70; // P3.4-6 = USCI_A0 TXD,RXD; USCI_A1 CLK

. . .

P5SEL = 0xEC; // Enable XT2 Ports, Enable USCI_A1 SIMO,SOMI

. . .

// Clock Setup

UCSCTL6 &= ~XT2OFF; // Enable XT2

UCSCTL3 |= SELREF_2; // FLLref = REFO

UCSCTL4 |= SELA_2; // ACLK=REFO,SMCLK=DCO,MCLK=DCO

do // Loop until XT1,XT2 & DCO stabilizes

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + XT1HFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

UCSCTL6 &= ~XT2DRIVE0; // Decrease XT2 Drive according to expected frequency

UCSCTL4 |= SELS_5 + SELM_5; // SMCLK=MCLK=XT2

. . .

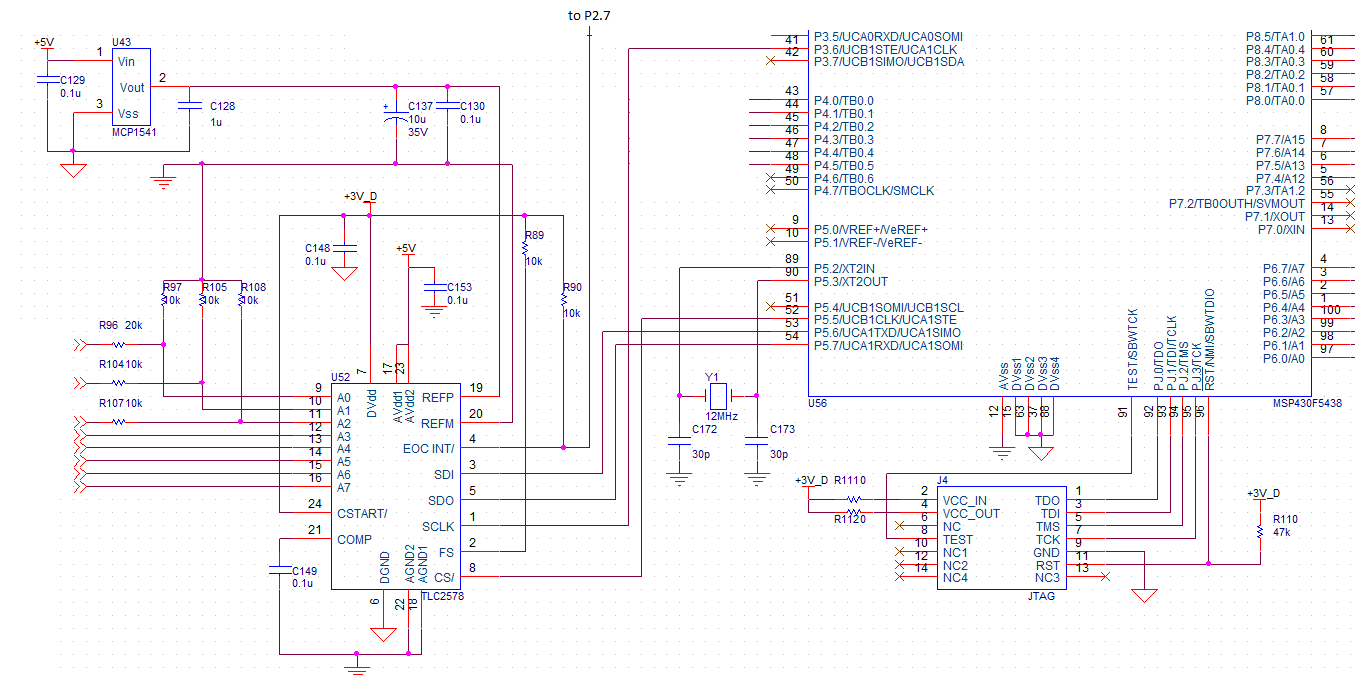

// TLC2578 Setup

UCA1CTL1 |= UCSWRST; // **Put state machine in reset**

UCA1CTL1 |= UCSSEL_2; // SMCLK

UCA1CTL0 |= UCMSB + UCMST + UCSYNC + UCMODE_2; // Synchronous, Master, MSB First, 4-pin AL

UCA1CTL1 &= ~UCSWRST; // Starts state machine

. . .

// Timer Setup

TA0CCTL0 = CCIE; // Interrupt Mode

TA0CCR0 = 49152-1; // 49152 cycles -> 3 s timer

TA0CCTL1 = CCIE; // Interrupt Mode

TA0CCR1 = 8192-1; // 8192 cycles -> 0.5 s timer

TA0CCTL2 = CCIE; // Interrupt Mode

TA0CCR2 = 12288-1; // 12288 cycles -> 0.75 s timer

TA0CTL = TASSEL_1 + MC_1 + ID_1 + TACLR; // ACLK, up, Input Divider = 2, clear TAR

. . .

// TLC2578 Init

unsigned char trash;

UCA1TXBUF = 0xAA; // Sends bits 15-8

while(!(UCA1IFG & UCTXIFG))

trash = UCA1RXBUF;

UCA1TXBUF = 0x40; // Sends bits 7-0

while(!(UCA1IFG & UCTXIFG))

trash = UCA1RXBUF;

. . .

#pragma vector=TIMER0_A0_VECTOR

__interrupt void TIMER0_A0_ISR(void)

{

unsigned char trash;

// TLC2578 Trigger Sequence

UCA1TXBUF = 0x08; // Sends bits 15-8

while(!(UCA1IFG & UCTXIFG))

trash = UCA1RXBUF;

UCA1TXBUF = 0x40; // Sends bits 7-0

while(!(UCA1IFG & UCTXIFG))

trash = UCA1RXBUF;

// Internal ADC Trigger Sequence

ADC12CTL0 |= ADC12SC; // Start internal ADC conversion

}

. . .

#pragma vector=TIMER0_A1_VECTOR

__interrupt void TIMER0_A1_ISR(void)

{

int data1 = 0;

int data2 = 0;

UCA1TXBUF = 0xE8; // Sends bits 15-8, FIFO Read

while(!(UCA1IFG & UCTXIFG))

data1 = UCA1RXBUF; // Store bits 15-8

UCA1TXBUF = 0x00; // Sends bits 7-0

while(!(UCA1IFG & UCTXIFG))

data2 = (UCA1RXBUF & 0xF0); // Store bits 7-4, discard 3-0

V27Supply = (data1*256+data2)/16; // Combine into 12-bit result

*(This is repeated for multiple channels)

}

Any help would be appreciated.