Part Number: ADS8339EVM-PDK

Other Parts Discussed in Thread: ADCPRO, ADS8339

Tool/software:

Hello

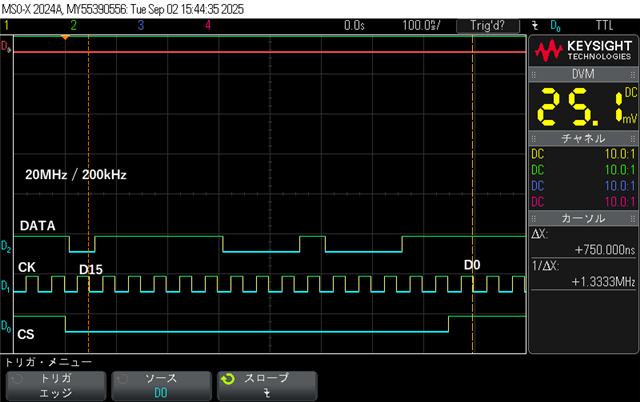

When DC is applied to the ADS8339EVM-PDK evaluation board, the conversion data changes depending on the settings.

Since the DC voltage contains noise from electronic circuits, the converted data is expected to be normally distributed.

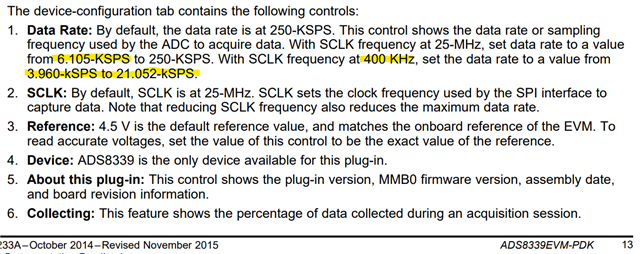

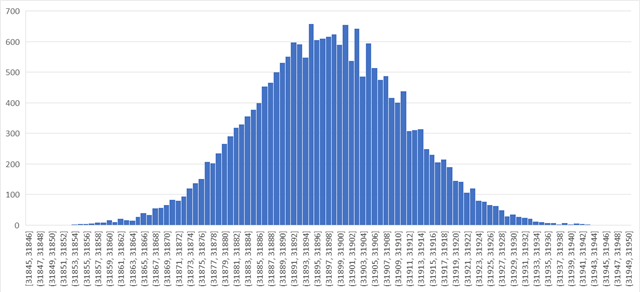

Data Rate 250kHz / SCLK 25MHz

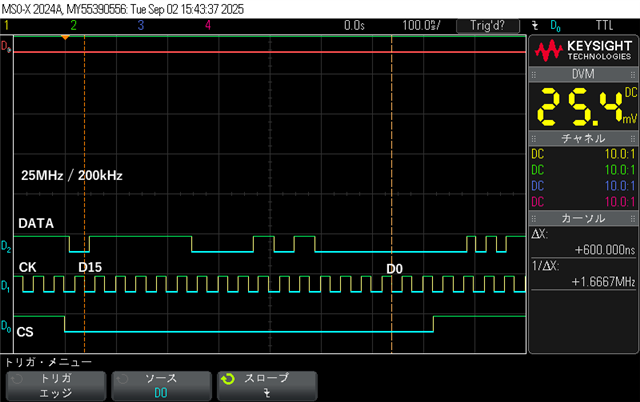

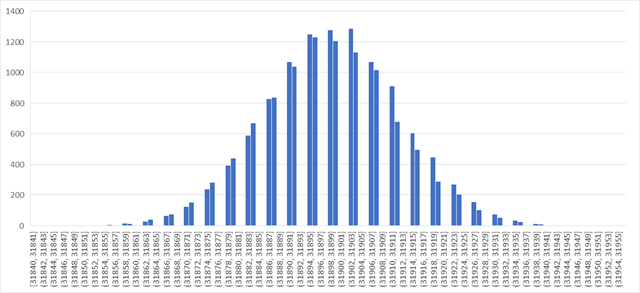

Data Rate 5kHz / SCLK 5MHz

Why does this happen when changing settings while the input signal remains the same?