Other Parts Discussed in Thread: ADS9815

Tool/software:

Hi team,

There are several questions. Could you please support these?

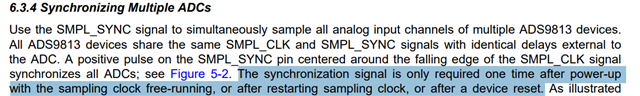

1. Regarding synchronization by using SMPL_SYNC pin, is it OK that the signal is required to the pin at just one time as described in the datasheet below?

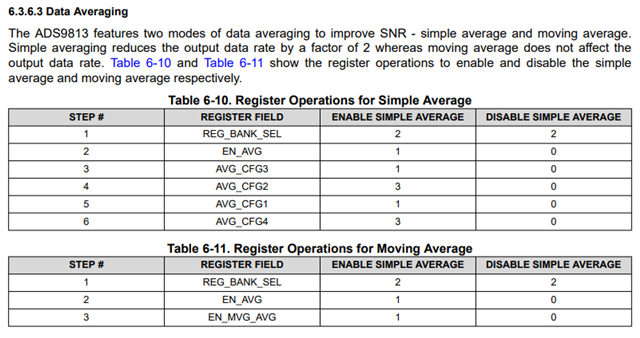

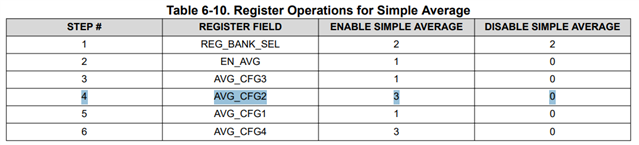

2. Does the device has oversampling function?

3. tDCLK at DDR mode is 10nsec at min, that is the frequency is 100MHz. Do you recommend to make the fequecny less than 100MHz considering the margin like temperature variance and so on?

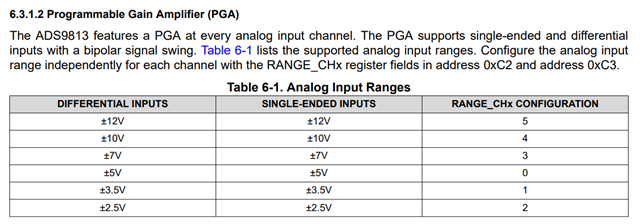

4. Does the device has any functions to adjsut gain value, phase and offset value after data conversion?

Regards,

Noriyuki Takahashi