Tool/software:

Hello everyone,

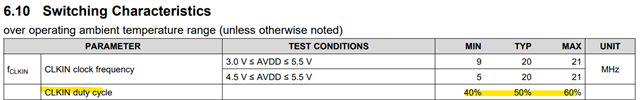

the datasheet specifies that the typ. CLKIN duty cycle is 50%. The limits for CLKIN are speficied with min 40% and 60% max.

What would happen if these values were not fullfilled, for example, a positive duty cycle of 30% was used?

Does this affect the overall function, or does the ADC simply become inaccurate?

Thanks all lot in advance!

Andreas