Tool/software:

I am currently having trouble enabling the REG_CRC bit. When I have the bit enabled, I am always receiving the REG_ERR flag.

I was able to enable the SPI_CRC and use the SPI transactions successfully without getting a SPI_ERR flag but seem to be having more of an issue using the register CRC feature.

Assumptions:

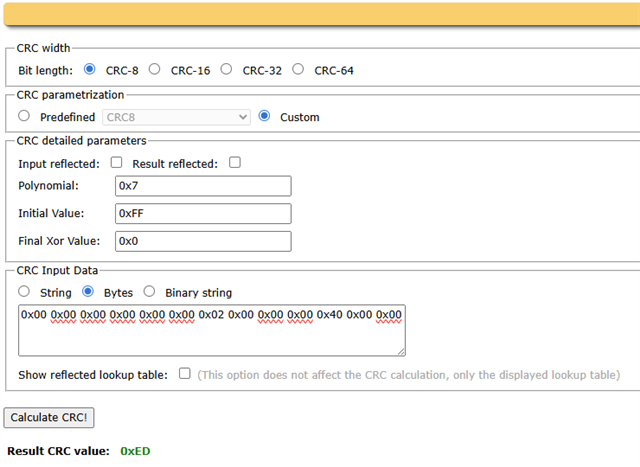

The datasheet says to calculated registers 0x00 to 0x01 with registers 0x04 to 0x0E. I am assuming I am to calculate the crc of all of the bytes in order from 0x00 to 0x0E (omitting 0x02 and 0x03). I am also assuming that the crc init should be 0xFF as that is what the SPI crc calculation requires. I am also assuming that this check should be performed after all of the registers have been set.

After all the registers have been set, I set a 10ms delay before writing to the status register to attempt to clear the REG_ERR flag. However, the error flag is still present.

To attempt to simplify the problem, can someone provide the expected value to place in this CRC field? If I set all values to default except CONFIG4 register, what should the expected CRC be?

uint8_t reg_val[13] = {

0x00, // Address 0x00 for DEV_ID

0x00, // Address 0x01 for CONFIG4, based on read REV_ID

0x00, // Address 0x04 for CONFIG4

0x00, // Address 0x05 for CONFIG4

0x00, // Address 0x06 for CONFIG4

0x00, // Address 0x07 for CONFIG4

0x02, // Address 0x08 for CONFIG4, setting the REG_CRC bit

0x00, // Start of offset values

0x00,

0x00,

0x40, // Start of gain values, default value per reference manual

0x00,

0x00

};

Using the sunshine2k crc tool: Sunshine's Homepage - Online CRC Calculator Javascript

I would expect a valid crc field would be 0xED

I was also having trouble finding examples online of how to implement this register check to confirm I am performing the correct operations. I am assuming TI has a unit test somewhere for this they can provide as a guide.