Tool/software:

Hi team,

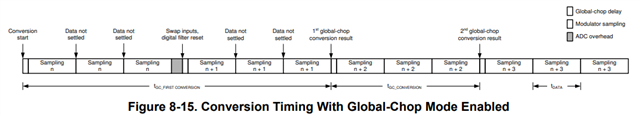

Customer have inquiry on the Global-chop mode.

If using Global-Chop Mode, it will measure three sampling (n), three sampling (n+1), three sampling (n+2) times, and so on.

This is the average of the three data obtained. Does this mean that offset correction is applied between the average values?

Or does it use the last value of three samples of sampling (n)?

Best regards,

Hayashi