Other Parts Discussed in Thread: AMC131M02

Tool/software:

Hi,

we had trouble initializing the AMC130M02 according the procedure described in datasheet.

We should:

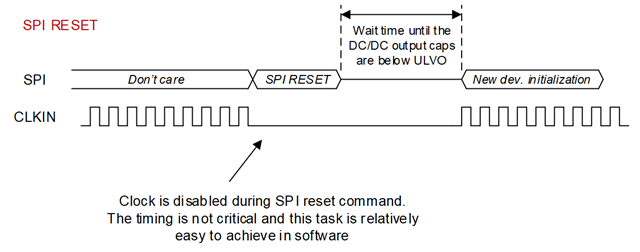

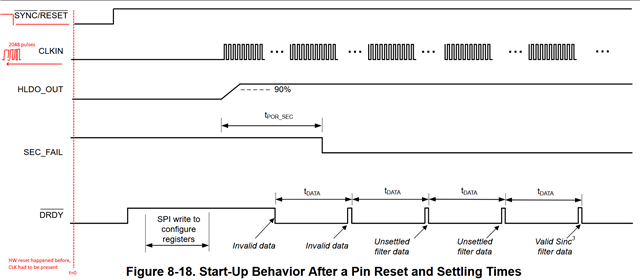

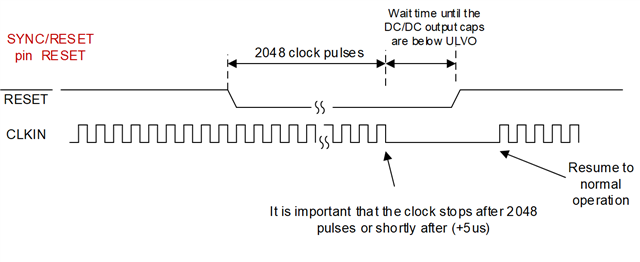

- disable the CLKIN signal

- do a long pulse on reset

- wait for DRDY to become high

- configure registers

- enable CLKIN signal

But it happened often that the DRDY signal got stuck low and never got to a high state. What works for us is to:

- enable CLKIN signal

- do a long pulse on reset

- wait for any change in DRDY

- disable CLKIN

- configure registers

- enable CLKIN

Would you have any hints on why the DRDY can get stuck low?

Is our procedure safe? It seems to be, but perhaps there are some risks that we missed.