Other Parts Discussed in Thread: ADS9229, ADS9228

Tool/software:

Hi

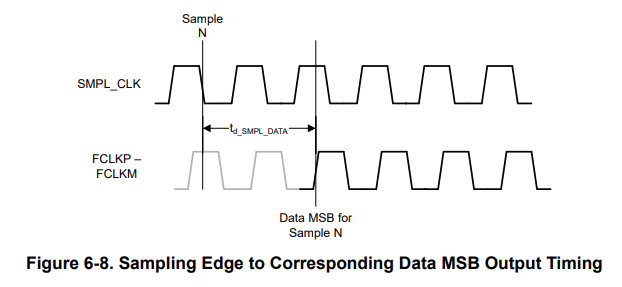

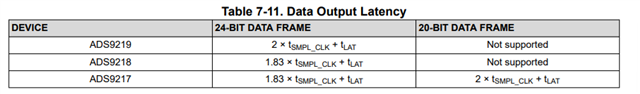

Section 6.7 of the ADS9227 datasheet lists the parameter Td_SMPL_DATA (Time delay: SMPL_CLK falling to FCLKP rising) as a minimum of 103ns and a maximum of 112ns.

Would it be correct to say that this value is only true when operating with a clk output period of 4.167ns and with a 24bit output word format? (24 x 4.167ns =100ns approx) . The paragraph preceding the table does say "maximum throughput", so I'm assuming that there is 3ns to 12ns of additional latency.

Would it then be correct to say that the additional latency is therefore independent of data link configuration and this 3ns -12ns would apply to any configuration of the ADC?

Many thanks for your help!