Other Parts Discussed in Thread: DAC38J84

Tool/software:

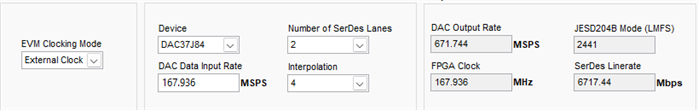

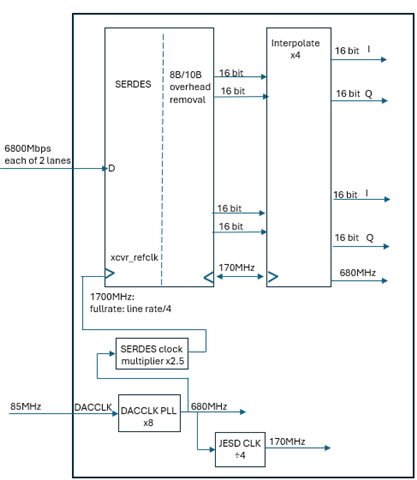

We are transmitting 170Msps x 64 across two JESD lanes as shown below (16 bit I/Q for each of two DAC outputs)

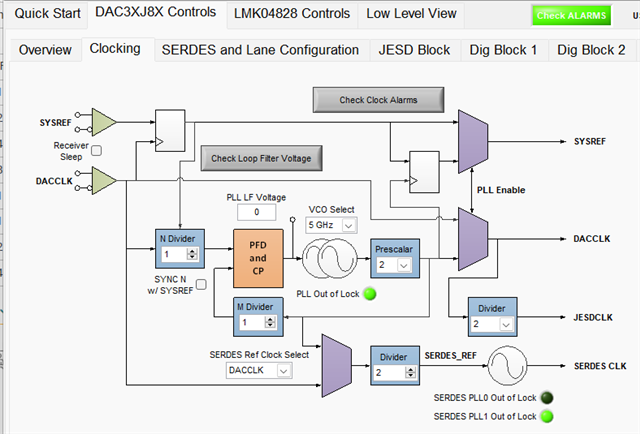

My assumption is that the JESDCLK should be 170MHz (divide by 4, config37=0x4000) as shown below.

However, it must be set to 340MHz (divide by 2, config37=0x2000) to work.