Tool/software:

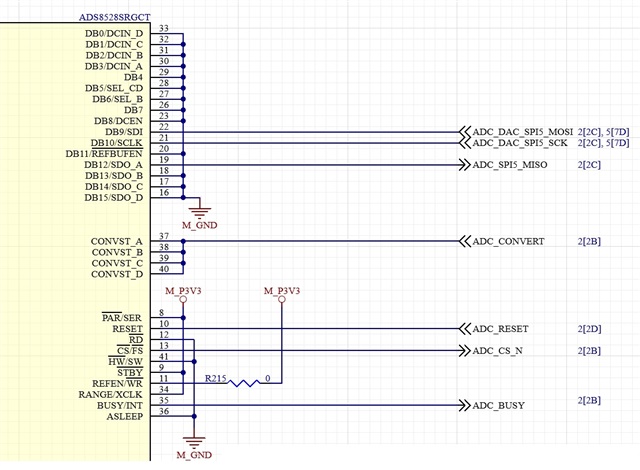

We are using the ADS8528 in HW configuration mode with serial data transfers.

See schematic for SPI connections.

From the datasheet, it appears the ADS8528 channels (CH_A0, CH_A1, CH_B0, CH_B1, CH_C0, CH_C1, CH_D0, CH_D1) are grouped as pairs and the data can be off-loaded serially in pairs via the SDO_A, SDO_B, SDO_C, and SDO_D outputs. Our design is configured to output all 8 channels serially via the SDO_A output.

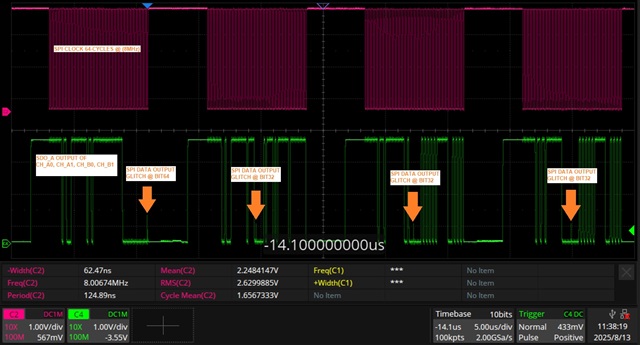

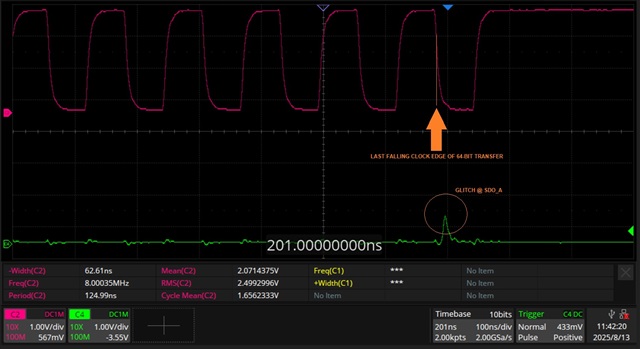

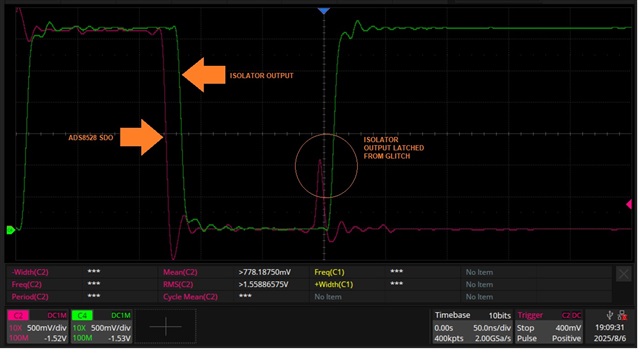

When reading the serial data output, there appears to be a “glitch” at the 32-bit and 64-bit boundary of the data transfer.

I have attached scope plots of the SPI clock and serial data output at SDO_A. While we are sampling all 8 channels, for this instance, we only read the first four channels (CH_A0, CH_A1, CH_B0, CH_B1). Therefore, these plots display groups of 64-bit transfers (channels CH_A0, CH_A1, CH_B0, and CH_B1).

Could the ADS8528 be the source of the “glitch”?

Is it possible that the glitch is an artifact of the ADS8528 any internal register switching that allows all channels to be output via the single SDO_A port?