Tool/software:

Hi everyone,

I work currently on a project which integrate an AFE58JD48 in our board. I use an FPGA to do SPI communication with the AFE58JD48.

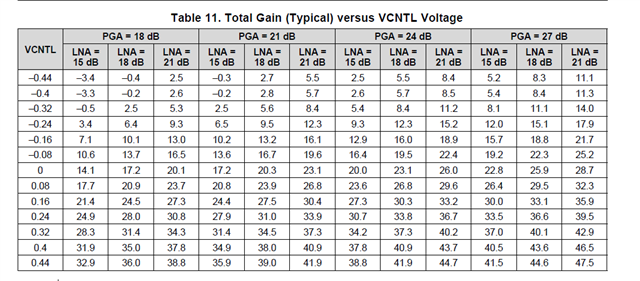

-> when I write register on VCA part (addr 0xC5 to 0x75E4), (addr 0xd1 to 0x588c), to set LNA=15DB,PGA=18DB,VCNTL=-0.31V, The corresponding total gain in the picture is 0DB, but my actual simulation is -6DB.

Under the settings of other LNAs, PGAs, and VCATs, the total gain is always 6dB less.

I couldn't find any more registers that need to be configured in the manual. How should I correctly configure the VCA registers? Could you provide me with a correct configuration?

Thanks for your help