Part Number: ADC32RF55

Other Parts Discussed in Thread: ADC12DJ2700, LMK04832

Tool/software:

Dear Person in Charge,

I am going to make a board using ADC32RF55 and evaluate its performance.

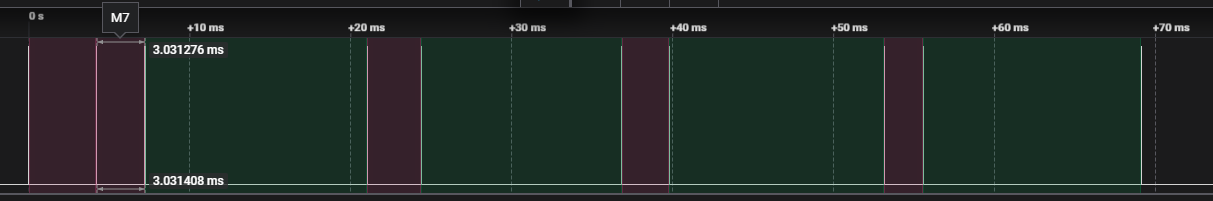

I have a question about the timing of SYSREF and device clock.

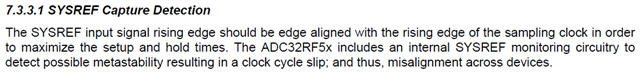

According to the section 7.3.3.1 of the ADC datasheet, it seems to mean that the rising edge of SYSREF should be aligned with the rising edge of device clock. Is this understanding correct?

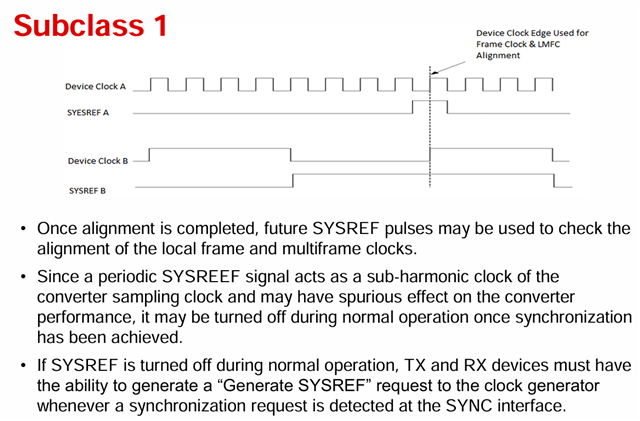

On the other hand, looking at TI's other documentation, it appears that SYSREF is being triggered when the device clock falls.

Which is correct?

Thank you.

Best regards,

Sayaka Kose