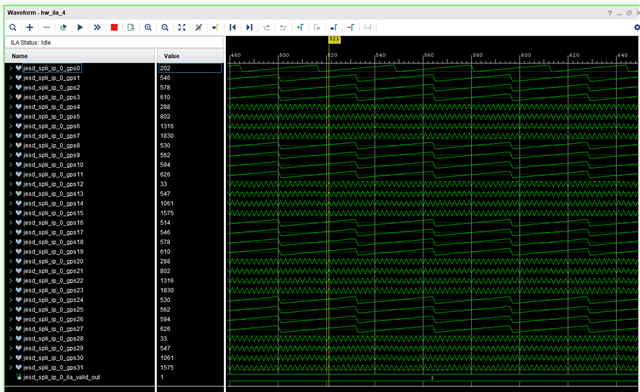

Tool/software:

We are ramp testing JESD on ADC12QJ800.

Output of JESD (withing FPGA using Vivado) looks like this:

Is this correct for half of the lanes to have different ramp period?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

We are ramp testing JESD on ADC12QJ800.

Output of JESD (withing FPGA using Vivado) looks like this:

Is this correct for half of the lanes to have different ramp period?