Other Parts Discussed in Thread: TSW14J58EVM, ,

Tool/software:

The ADC is evaluated using ADC32RF55EVM and TSW14J58EVM.

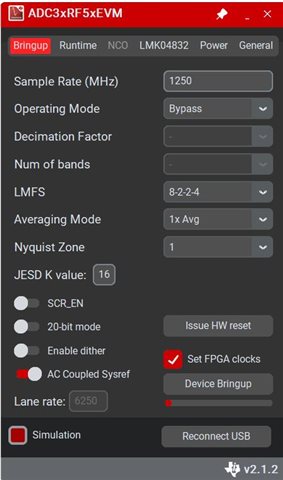

ADC3xRF5xEVM-GUI tool is used to set the register to ADC.

I have the following questions.

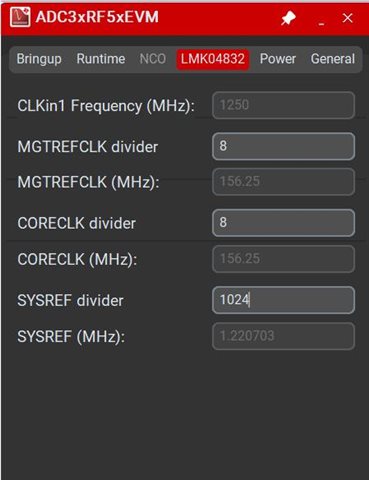

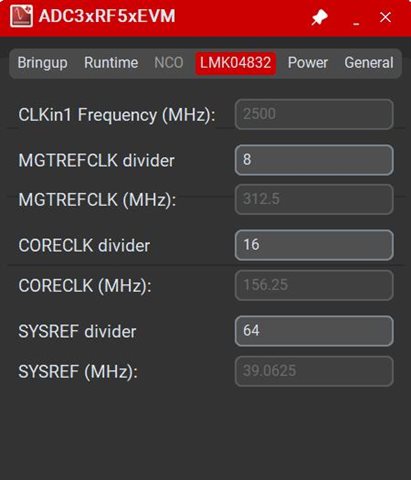

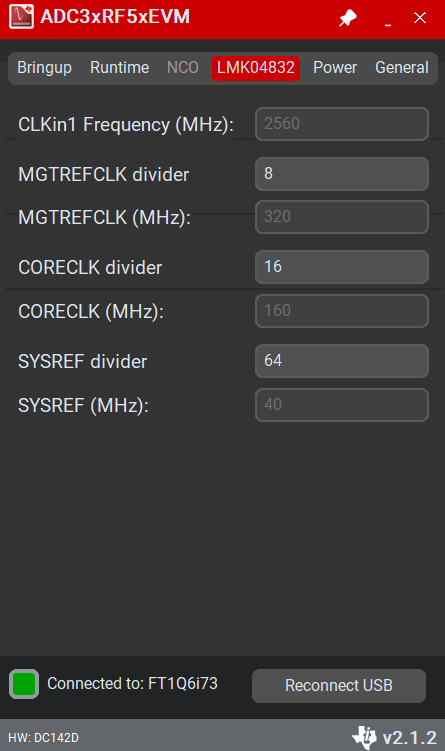

① I want to run FPGA with original implementation, but the value of divider in LMK setting is automatically 8/16/64 when BringUP. Do I have to change the receiver (FPGA) with this condition?

Why is it forced to this value during BringUP? Is the reason a constraint on the ADC32RF55 side? Or is it an EVM specific constraint?

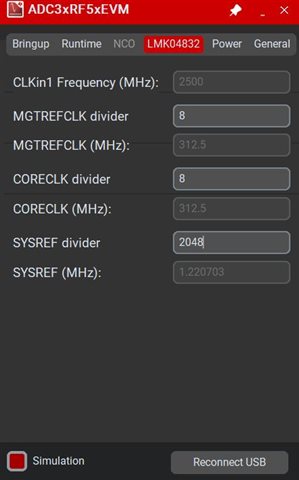

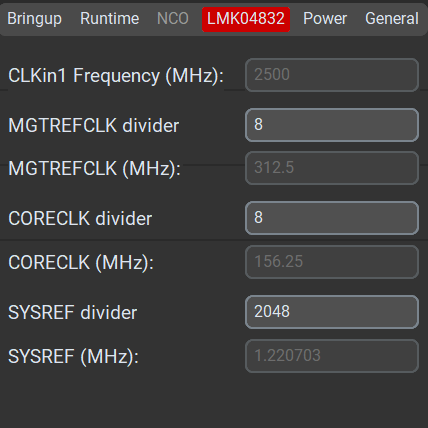

② I know that if I change the value of LMK page after BringUP, the value of SYSREF etc. will be changed. For example, if I want to proceed with the value of each divider at 8/8/2048, is there no problem with the following procedure? Is there any other necessary procedure?

[Procedure]

・Use ADC tool to DeviceBringUP

・Set LMK to 8/8/2048.

・Write FPGA to TSW・・・EVM evaluation board.

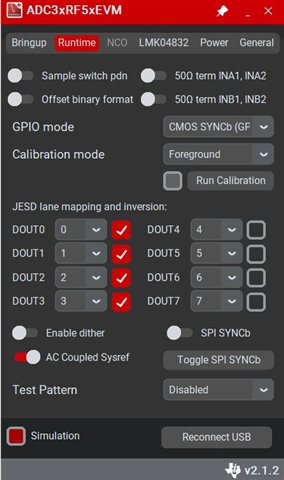

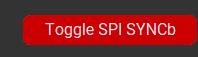

・Press Toggle SPI SYNCb.

③ When running ADC32RF55 using the original board, should the divider value of LMK setting be designed to be 8/16/64 during BringUP? Should we not design an arbitrary divider value from the beginning?

Thanks and best regards,

Sayaka Kose