Tool/software:

Hello,

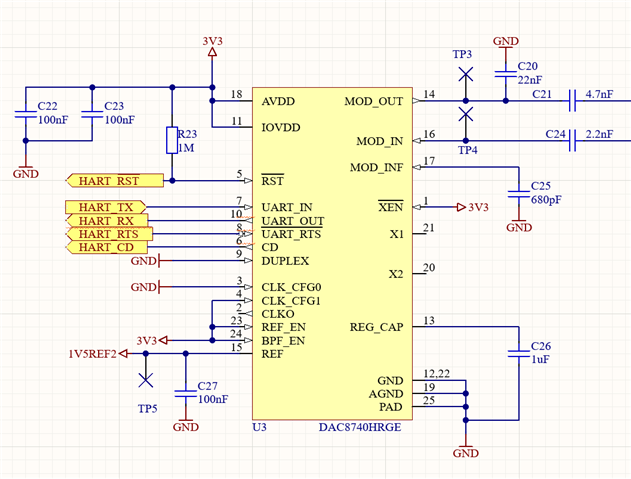

I'm building a HART field device (DUT) using the DAC8740H with UART. The Hardware is similar to the reference design Figure 34 in the datasheet (page 33).

I'm using a certified USB HART modem as a host which transmits HART FSK signals to the DUT. The Signal contains UART8O1 data. The error occurs on the last bytes 4 UART8O1 packages (last 4 bytes: 0xa3d70ac2).

However the UART signal on the DUT from the DAC8740H to the MCU has a lot of framing errors. Measuring the FSK signal with an oscilloscope shows me a correct signal:

C1 is the UART from the DAC8740H, M4 is the FSK measured between DAC8740H and C7 from the reference design. However M4 is delayed so that it is synchrone with the UART.

C2 is the FSK modulated on the 24V before the C7 and C4 is the FSK between DAC8740H and C7 without the delay.

When you look at the stop bit you can see a 1.2kHz FSK signal wich would translate to a high signal. Is this a problem with the modem? Has anyone else this problem?

Kind regards,

Nico