Tool/software:

Following:

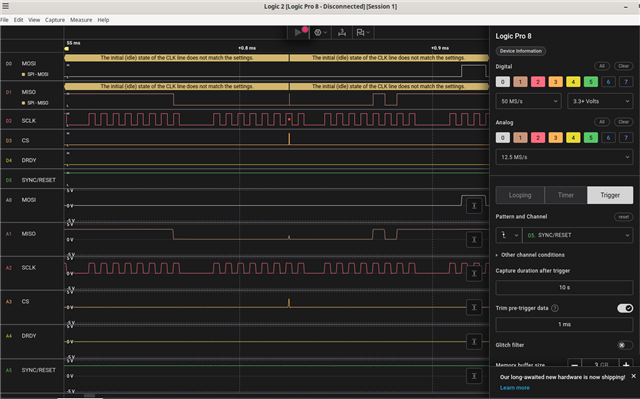

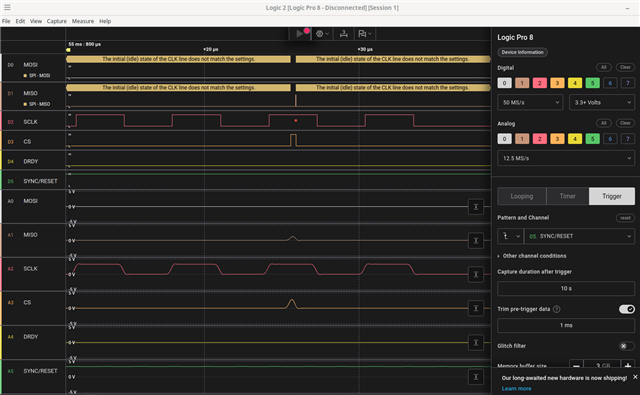

we have slowed the SCLK way down, but are still having problems. If you could please inspect the attached Salae session dump, I want to direct your attention to the first MOSI traffic and the errors denoted there. Somewhere about +25µsec. You will find there and odd red blip amid the SCLK signal, and you will also not a blip in the MISO that is much narrower than the traffic rate. It appears that it might be crosstalk from the CS signal, or are my eyes playing tricks on me? The logic analyzer declares that "The initial (idle) state of the CLK line does not match the settings." Thank you for any wisdom that you can share.Session1.sal.zip

Clark