Hi:

1. I have attached the following graphic from the ADS1259 datasheet tat shows it has 2 noise specs (~ 1uVrms and 6uVrms) for the 14.4Kbps datarate. Is this correct or a typo?

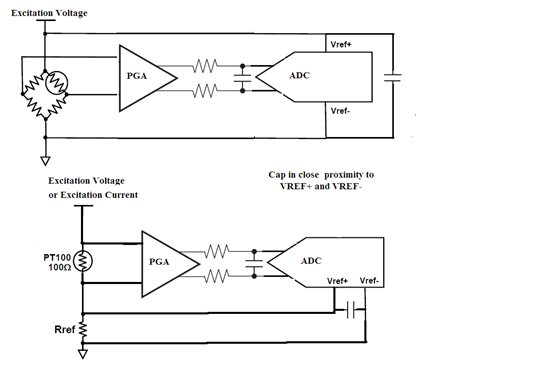

2. Also, how do i configure the ADC for use in a ratio-metric application as this is the most precise mode of operation for all output data rates?

3. When is the appropriate time to de-assert the START pin low? Is it after /DRDY is low or some other time?

4. Is there a way one can simulate the ADS1259 converter? If not, what is the closest ADC one could use in Spice for simulation?

Thanks,

David