Other Parts Discussed in Thread: LMK04828

Tool/software:

Hi,

When I am trying the configure the DAC39J84 I am observing my sync signal and

tx_tready signal are toggling. I am configuring the DAC with the following settings:

sampling rate = 500 MHz,

linerate = 5 GSPS,

DACCLK = 500 MHz,

JESD Ref clk = 125 MHz,

SYSREF = 1.953125 MHz,

LMFS = 8411,

K = 32

The device clock and SYSREF for the FPGA are given from LMK04828. The device clock for

the DAC (DACCLK) is given from the LO1 output of HMC835. The LO2 output of HMC835 is

given to HMC7043 divider, which has same frequency as that of LO1, from which the DAC SYSREF

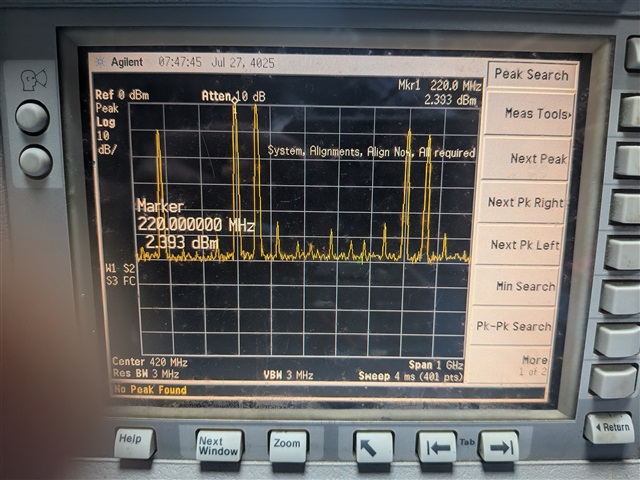

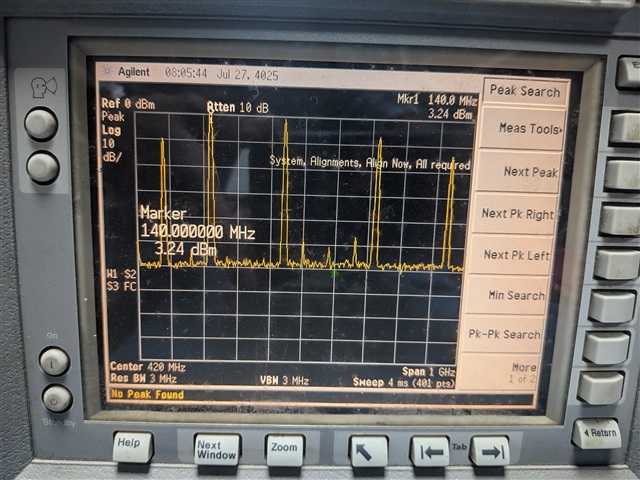

is generated. I have performed the NCO test for SYSREF and observed that the SYSREF is being

generated correctly i.e.I can observe multiple peaks.

The following registers are written for configuring the DAC -

ADDR DATA

0x00 0x001C

0x01 0x0800

0x02 0x2082

0x03 0xF080

0x04 0x00FF

0x05 0xFF0D

0x06 0xFFFF

0x07 0x0000

0x08 0x0000

0x09 0x0000

0x0A 0x0000

0x0B 0x0000

0x0C 0x0400

0x0D 0x0400

0x0E 0x0400

0x0F 0x0400

0x10 0x0000

0x11 0x0000

0x12 0x7000

0x13 0x7000

0x14 0x0000

0x15 0x0000

0x16 0x4000

0x17 0x0000

0x18 0x0000

0x19 0x4000

0x1A 0x0020

0x1B 0x0000

0x1E 0x1111

0x1F 0x99C0

0x20 0x8888

0x22 0x1B1B

0x23 0x01FF

0x24 0x0020

0x25 0x2000

0x26 0x0000

0x2D 0x0001

0x2E 0xFFFF

0x2F 0x0004

0x30 0x0000

0x31 0x7030

0x32 0x0700

0x33 0x7FC8

0x34 0x0000

0x3B 0x0800

0x3C 0x9028

0x3D 0x0088

0x3E 0x0108

0x3F 0x0000

0x46 0x0044

0x47 0x190A

0x48 0x31C3

0x49 0x5500

0x4A 0xFF1E

0x4B 0x1F00

0x4C 0x1F07

0x4D 0x0300

0x4E 0x0F6F

0x4F 0x1CC1

0x50 0x0000

0x51 0x00DF

0x52 0x00DF

0x53 0x0000

0x54 0x00FF

0x55 0x00FF

0x56 0x0000

0x57 0x00FF

0x58 0x00FF

0x59 0x0000

0x5A 0x00FF

0x5B 0x00FF

0x5C 0x1155

0x5E 0x0000

0x5F 0x0123

0x60 0x4567

0x61 0x0003

0x64 0x0000

0x65 0x0000

0x66 0x0000

0x67 0x0000

0x68 0x0000

0x69 0x0000

0x6A 0x0000

0x6B 0x0000

0x6C 0x0000

0x6D 0x0000

0x6E 0x6A70

0x6F 0x0325

0x70 0x076F

0x71 0x01D6

0x72 0x016E

0x73 0x5974

0x74 0xD6D8

0x75 0x7000

0x76 0x6A70

0x77 0x0325

0x78 0x076F

0x79 0x01D6

0x7A 0x016E

0x7B 0x5974

0x7C 0xD6D8

0x7D 0x7000

0x7E 0x0000

0x7F 0x0000

With these settings I am able to observe the sync and ready signals are toggling. I have verified

all the registers mentioned in the datasheet under " Initialization Set up" section. Is there any register

that needs to be configured or any other setting that needs to be considered to establish a stable link ?

Regards

P. Anirudh Reddy