Other Parts Discussed in Thread: LMK04832, LMX2594

Tool/software:

Hello TI Team,

I'm currently investigating the necessary CLK and sysref frequencies for our slated ADC12DJ5200RF JESD204C implementation. I would like some assistance with choosing these clock frequencies. Please assume I am using a TI LMK04832 for clock distribution and TI LMX2594 RF Synthesizer for ADC core frequency and sysref frequency generation.

The general flow I intend to have with my application is: 10 MHz input --> LMK04832 --> 10 MHz CLK and 10 MHz SYSREF outputs --> LMX2594 --> 5200 MHz CLK to ADC12DJ5200RF; 2.539 MHz SYSREF CLK to ADC12DJ5200RF.

For the CLK, I plan on using a 5.2 GHz input derived from the LMX2594 RF Synthesizer for the maximum dual-channel sample rate. My concern is how do I derive such a precise clock for SYSREF given my calculation came out to be 2.539 MHz? I've written out my calculation below.

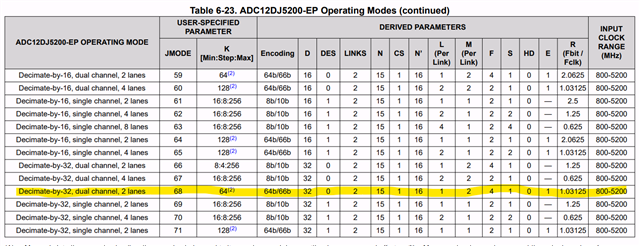

We plan on using the below highlighted JESD configuration. We plan on using the 1-shot approach for JESD synchronization.

fsysref = (R * fclk)/(66 * 33 * E * n)

fsysref = (1.03125 * 5200 MHz)/(66 * 33 * 1 * 1)

fsysref = 2.539 MHz

Does it matter if the clock is approximate, such as being 2.5 MHz? I've read that phase synchronization is more important than precise sysref frequencies in the 1-shot approach for JESD synchronization.

Any assistance is appreciated! Please let me know if you have any questions.

Regards,

Joseph Blank