Tool/software:

Hello TI Support Team,

I recently purchased the ADS8371 and am experiencing an issue that I would like to ask about.

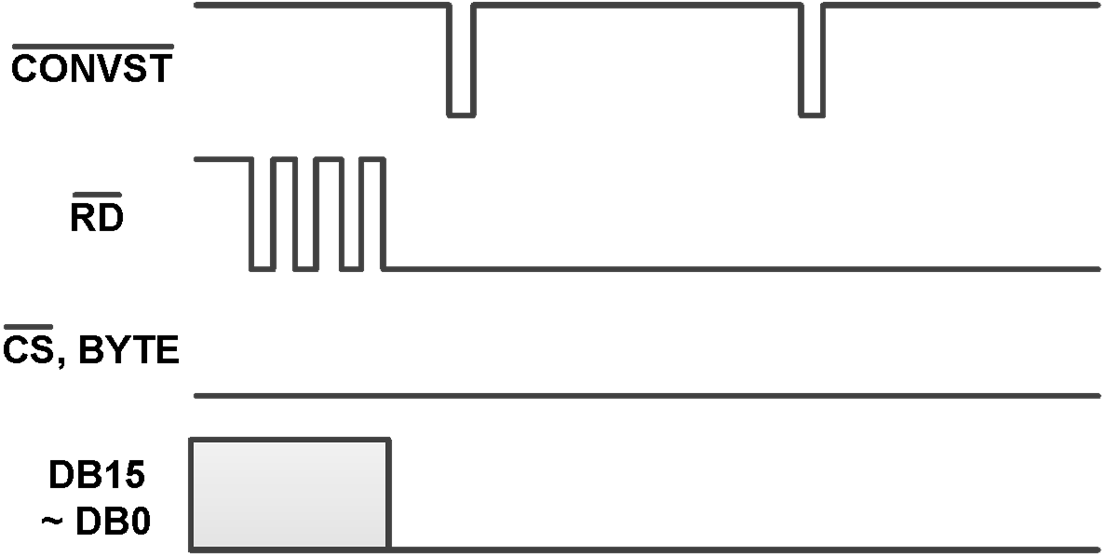

In order to minimize the number of control signals, I tied CS bar, RD bar, and BYTE to logical low, and generated only a low-toggling pulse on CONVST bar to sample the ADC input. However, I found that the ADC output remains fixed at a logical high level without changing.

According to the datasheet, RD should be toggled three times during initialization. Could the problem be caused because I did not perform this step? My understanding is that this step is only required to avoid invalid outputs from the first three conversions, and that if I only intend to use subsequent outputs, RD bar could be tied to ground. Could you please confirm whether this assumption is correct?

Thank you for your assistance.

Best regards,

Kihun Kim